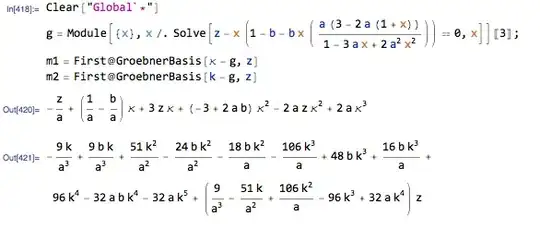

I am currently working on implementing a code that performs a right shift on a 23-bit array. However, I am facing some issues:

I'm not sure why, but when I visualize the 'din' signal using GTKWAVE, I always find a '0' at the beginning of my input signal. For example, if I input "11111111111111111111111" in my testbench, I get "01111111111111111111111" as the value of 'din' (input).

I added a clock signal because I was struggling to update the code correctly inside my process. My intention is to perform a right shift three times (using 'N = 3' as the input signal in the testbench). Despite my efforts, the current code does not produce the desired outcome.

Below, you'll find my code and testbench.

This is my current GTKWAVE result (I know, it's a mess). In particular you see that the first din signal is 7FFFFF = "01111111111111111111111", instead it should be "11111111111111111111111".

main code:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY shift_right IS

PORT (

clk : IN std_logic;

N : IN natural;

din : IN std_logic_vector (22 downto 0);

dout : OUT std_logic_vector (22 downto 0)

);

END ENTITY;

ARCHITECTURE shift_right OF shift_right IS

BEGIN

PROCESS(clk)

VARIABLE tmp : std_logic_vector(22 downto 0) := (OTHERS => '0');

BEGIN

tmp := din;

IF (clk'EVENT AND clk = '1') THEN

FOR i IN 0 TO N - 1 LOOP

tmp := '0' & tmp(21 downto 0);

END LOOP;

END IF;

dout <= tmp;

END PROCESS;

END ARCHITECTURE;

Testbench:

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.NUMERIC_STD.ALL;

entity shift_right_TB is

end entity;

architecture TESTB of shift_right_TB is

component shift_right is

PORT (

clk : IN std_logic;

N : IN natural;

din : IN std_logic_vector (22 downto 0);

dout : OUT std_logic_vector (22 downto 0)

);

end component shift_right;

signal din, dout : std_logic_vector(22 downto 0);

signal N : natural;

signal clk : std_logic := '0';

begin

-- Clock generation process

clk <= not clk after 5 ns;

-- Stimulus generation process

stimulus_generation : process

begin

wait for 30 ns;

N <= 3;

din <= "11111111111111111111111";

wait for 30 ns;

din <= "11111000011111111111111";

wait for 30 ns;

din <= "11111111111111111100000";

wait for 30 ns;

din <= "10101010101010101010101";

wait for 300 ns;

end process stimulus_generation;

-- Instantiate DUT (Design Under Test)

DUT : shift_right

PORT MAP(

clk => clk,

din => din,

dout => dout,

N => N

);

end architecture TESTB;

In summary, I'm puzzled by the presence of the leading '0' in every 'din' signal. Additionally, I dont'know how to properly set up the clock signal to ensure the accurate updating of the code within the process.