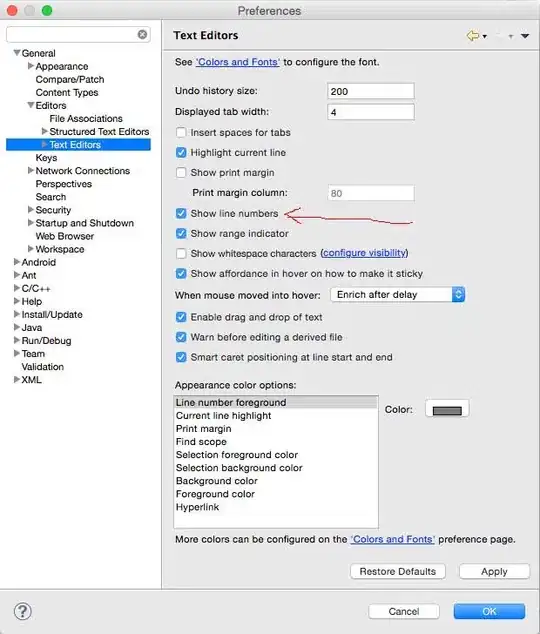

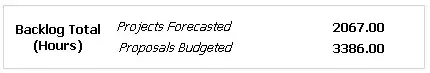

Since the control unit takes one input which is opCode, Jr and other R type instructions passes to 000000 to control unit. But for Jr, RegWrite must be 0. How does the control unit differentiate between Jr and the other R-type instructions if they have the same opCode? Do I need to pass funct code to control unit?

I'm working on a Mips Datapath simulator. I have implemented the control unit using a logic design I found in a Computer Architecture lecture notes from a university. You can ignore the AluOp for now.

this.outputs[0].changeValue(opCode == "000000"); // regdest

this.outputs[1].changeValue(opCode == "000010" || opCode == "000011"); //jump

this.outputs[2].changeValue(opCode == "000100"); //branch

this.outputs[3].changeValue(opCode == "100011"); //memread

this.outputs[4].changeValue(opCode == "100011"); // memtoreg

this.outputs[5].changeValue(

["000000"].includes(opCode)

? "10"

: ["100011", "101011"].includes(opCode)

? "00"

: opCode == "000100"

? "01"

: "11" //X

); //aluop

this.outputs[6].changeValue(opCode == "101011"); //memwrite

this.outputs[7].changeValue(opCode != "000000" && opCode != "000100"); //alusrc

this.outputs[8].changeValue(

!["101011", "000010", "000100"].includes(opCode)

); //regwrite

Here is the current version of the simulator: https://saliherdemk.github.io/Mips-Datapath-Simulator/

I searched for a more complex, geniune logic for control unit but I didn't find. Standard datapath needs to modification for JR instruction but I didn't find anything about inside of the control unit.

Edit

Jr datapath looks like this. But since opCode is same it jumps to address in the rd register for all R type instructions. Do we need to pass func code to the control unit?