I want to work on ADC (ads8556). In Figure 3 In the Parallel Read Access Timing Diagram, when the conversion time (tconv) finishes, and during the acquisition time (tACQ), there are multiple transitions in the level state of convst signal changes between 0 and 1. This transition between 0 and 1 is not clear for me. Can anyone tell me if it is optional or not?

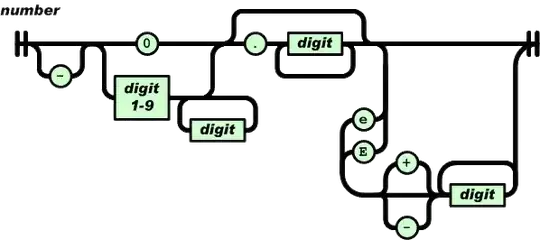

The timing diagram is shown in the figure.

I am working of ads8556 with FPGA de2i-150. But I don't understand the timing diagram.