I am implementing a door lock that requires user password. I have implemented states to identify predefined passwords of 123, 122, and 121, and it unlocks the door after the correct password is entered sequentially. I am implementing this door lock using four push buttons (KEY0 as digit '1', KEY1 as digit '2', KEY2 as digit '3', and KEY3 as digit '4') and a reset, RST (assigned to SW0) on DE1-SoC FPGA board. The link of user manual is below: http://www.ee.ic.ac.uk/pcheung/teaching/ee2_digital/de1-soc_user_manual.pdf

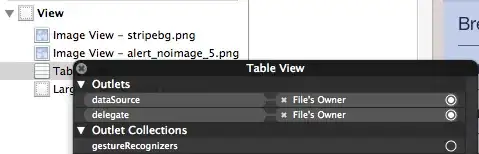

Please refer to the attached image for the states diagram

.

.

I am facing a problem in which whenever KEY0 push button on the board (at S0 initially) is pressed, it would instantly go to S8(displayed on the seven segment). Is there something wrong with my code? Do note that the push button on DE1-SoC Board is active low.

HEX0 and HEX1 are actually assigned to two seven-segment displays on the board.

Below is my Verilog code:

module rewardsys(KEY0,KEY1,KEY2,KEY3,HEX0,HEX1,RST);

input KEY0,KEY1,KEY2,KEY3,RST;

output reg [6:0] HEX0,HEX1;

parameter s0=4'b0000;

parameter s1=4'b0001;

parameter s2=4'b0010;

parameter s3=4'b0011;

parameter s4=4'b0100;

parameter s5=4'b0101;

parameter s6=4'b0110;

parameter s7=4'b0111;

parameter s8=4'b1000;

reg[3:0] cstate,nstate;

always@(posedge KEY0,posedge KEY1,posedge KEY2,posedge KEY3,negedge RST) begin

if(RST==0)

cstate<=s0;

else

cstate<=nstate;

end

always @ (posedge KEY0,posedge KEY1, posedge KEY2, posedge KEY3) begin

case(cstate)

s0:

begin //display S0

HEX1=7'b0010010;

HEX0=7'b1000000;

if(KEY0==0)

nstate=s1;

else if ((KEY1==0) | (KEY2==0) | (KEY3==0))

nstate=s6;

else

nstate=s0;

end

s1:

begin //display S1

HEX1=7'b0010010;

HEX0=7'b1111001;

if(KEY1==0)

nstate=s2;

else if ((KEY0==0) | (KEY2==0) | (KEY3==0))

nstate=s7;

else

nstate=s1;

end

s2:

begin //display S2

HEX1=7'b0010010;

HEX0=7'b0100100;

if(KEY2==0)

nstate=s3;

else if(KEY1==0)

nstate=s4;

else if(KEY0==0)

nstate=s5;

else if(KEY3==0)

nstate=s8;

else

nstate=s2;

end

s3:

begin //display S3

HEX1=7'b0010010;

HEX0=7'b0110000;

end

s4:

begin // display S4

HEX1=7'b0010010;

HEX0=7'b0011001;

end

s5:

begin //display S5

HEX1=7'b0010010;

HEX0=7'b0010010;

end

s6:

begin //display S6

HEX1=7'b0010010;

HEX0=7'b0000010;

if ((KEY0==0) | (KEY1==0) | (KEY2==0) | (KEY3==0))

nstate=s7;

else

nstate=s6;

end

s7:

begin //display S7

HEX1=7'b0010010;

HEX0=7'b1111000;

if ((KEY0==0) | (KEY1==0) | (KEY2==0) | (KEY3==0))

nstate=s8;

else

nstate=s7;

end

s8:

begin //display S8

HEX1=7'b0010010;

HEX0=7'b0000000;

nstate=s8;

end

default:

nstate=s0;

endcase

end

endmodule

Thank you in advance.