I'm trying to execute for a synchronous driver, I aligned the driven signals to the clock edge as the below. I used nonblocking assignment to avoid race conditions in the UVM driver.

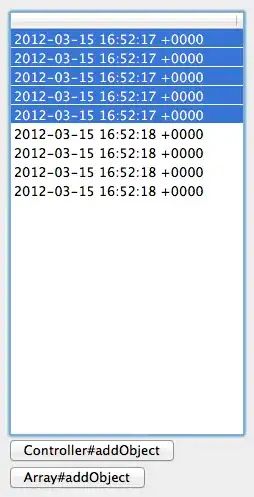

When I ran the driver, I got this printed out:

myCmd.start: 1

myCmd.start: 0

but, I expected as the below:

myCmd.start: 0

myCmd.start: 1

In the waveform viewer, I have checked the signal is correctly working.

Only uvm_info() is not working correctly. If I add #1

#1; uvm_info(get_type_name(), $sformatf("myCmd.start:%h", my_master_vif.dut_command), UVM_LOW)

then I can print the correct value.

Is this not enough to handle the race condition for uvm_info() in the driver? How can I avoid this problem?

class my_master_driver_c extends uvm_driver#(my_frame_c);

virtual my_if my_master_vif;

//...

task run_phase(uvm_phase phase);

while (1) begin

begin

forever begin

@(posedge my_master_vif.dut_clock_i iff (my_master_vif.reset))

seq_item_port.get_next_item(req);

drive_transfer(req);

#10;

seq_item_port.item_done(req);

end

end

end

endtask

//...

task drive_transfer (input my_frame_c trans);

@(posedge my_master_vif.dut_clock_i iff (my_master_vif.reset));

my_master_vif.dut_command <= 0;

`uvm_info(get_type_name(), $sformatf("myCmd.start:%h", my_master_vif.dut_command), UVM_LOW)

@(posedge my_master_vif.dut_clock_i iff (my_master_vif.reset));

my_master_vif.dut_command <= 1;

`uvm_info(get_type_name(), $sformatf("myCmd.start:%h", my_master_vif.dut_command), UVM_LOW)

//...

endtask : drive_transfer

//...

endclass

This is my interface:

interface my_if

(

input clock_my,

reset,

inout wire w_dut_command,

output reg dut_clock_i,

//...

);

timeunit 1ps;

timeprecision 1ps;

assign dut_clock_i = clock_my;

logic dut_command = 'bz;

assign w_dut_command = dut_command;

clocking driver_cb @(posedge clock_my);

default input #1 output #1;

inout dut_command;

endclocking

endinterface : my_if