I am trying to write some simple Verilog code for practice reasons. I am using the FPGA Cyclone 4. My 8-bit counter works fine with the on-board clock (50MHz), but it's way too fast to see the LEDs at that speed, so I tried first to slow the clock with this:

module enableCounter(

input clock_5,

input reset,

output reg enable_out);

reg [3:0] counter;

always @(posedge clock_5) begin

if (reset) begin

counter <= 4'b0000;

end

else begin

counter <= counter + 1;

if (counter == 4'b0000)

enable_out <= 1;

else

enable_out <= 0;

end

end

endmodule

Technically this would set the enable_out output to 1 only 8th of clock_5 time. To count Up and Down I wrote also this function:

module updown_counter(

input up_down,

input clk,

input enable,

input reset,

output reg [7:0] count_out);

always @ (posedge clk) begin

if (up_down == 0) begin // Count UP

if (reset)

count_out <= 8'b0000_0000;

else if (enable && count_out == 8'b1111_1111)

count_out <= 8'b0000_0000;

else if (enable && count_out != 8'b1111_1111)

count_out <= count_out + 8'b0000_0001;

else

count_out <= count_out;

end

else if (up_down == 1) begin // Count DOWN

if (reset)

count_out <= 8'b1111_1111;

else if (enable && count_out == 8'b0000_0000)

count_out <= 8'b1111_1111;

else if (enable && count_out != 8'b0000_0000)

count_out <= count_out - 8'b0000_0001;

else

count_out <= count_out;

end

end

endmodule

There is no compilation error. The 8 LEDs (connected to count_out) are off and turn all on, when I press the button for reset. I also tried changing some value like the up_down direction, just to check if its a button fault, but it did the opposite, which indicates, that there's a bug in my program (I guess?)

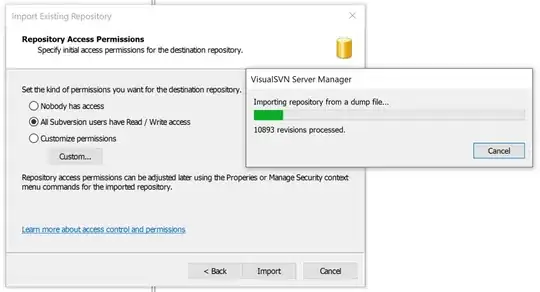

Edited: Using .bdf in Quartus, the connection from on-board clock to pll-block and then to the modules is shown here: