I try to get an UART IP core in combination with the NIOS2 (softcore) running on the Cyclone 10 LP evaluation board. So far everything works fine in polling mode. However, I cannot manage to get the interrupts running on the softcore.

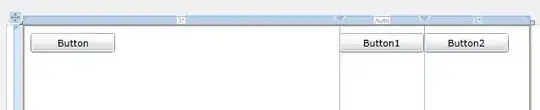

The FPGA is configured in the following way.

From the picture it can be seen, that the interrupt line is connected to the NIOS2 softcore processor.

The following picture shows that the Altera UART driver is available.

The initalization code provided by Altera looks like the following.

/*

* Initialize the interrupt controller devices

* and then enable interrupts in the CPU.

* Called before alt_sys_init().

* The "base" parameter is ignored and only

* present for backwards-compatibility.

*/

void alt_irq_init ( const void* base )

{

ALTERA_NIOS2_GEN2_IRQ_INIT ( NIOS2E, nios2e);

alt_irq_cpu_enable_interrupts();

}

/*

* Initialize the non-interrupt controller devices.

* Called after alt_irq_init().

*/

void alt_sys_init( void )

{

ALTERA_AVALON_JTAG_UART_INIT ( JTAG_UART, jtag_uart);

ALTERA_AVALON_UART_INIT ( UART_0, uart_0);

ALTERA_REMOTE_UPDATE_INIT ( REMOTE_UPDATE_0, remote_update_0);

}