Hello everyone I wrote some VHDL code that implement a UART-TX from my FPGA to my desktop. To trigger data sending I use the signal(debounced ofc) coming from the on-board switch.

As long as the button is pressed data is being sent. Inevitably, for as quick as I can be pushing and releasing this switch, the FPGA sends many UART packet duplicates to the laptop. This is because i directly connected the button signal to the start bit of the UART-TX entity. Therefore, I removed this direct connection and instead use the button to actually generate a short bit pulse to trigger the UART-TX entity just once.

So I did this:

--start_deb is the start bit (debounced? coming from the switch

i_TX_DV_gen: process(start_deb, clk) is

variable counter: natural := 0;

begin

if rising_edge(start_deb) then

i_TX_DV <= '1';

end if;

if i_TX_DV = '1' and rising_edge(clk) then

counter := counter + 1;

if counter > 10_000 then

i_TX_DV <= '0';

counter := 0;

end if;

end if;

end process;

So the trigger bit to the UART entity is set to '1' when I press the button and then after a number of clock cycles (which I unsured smaller than the ones necessary to send one packet) it goes to '0' again avoiding the send any duplicates.

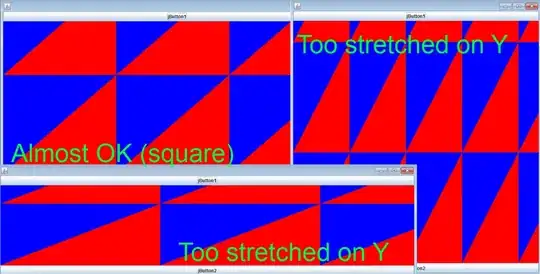

This works in simulation, I attached the waveform:

These are the signals description

clk:system clock

start_n: button signal (pressed when low)

start: not(start_n)

shift_input_n: button signal to select the next byte code.

o_TX_serial: serial output of the TX entity

packet: byte to be sent

i_TX_DV: trigger bit to start UART-TX trasmission

start_deb: start signal but debounced

The problem is that when I download it to my FPGA, the i_TX_DV is set to '1' only the first time.

[ To visualize this I used a FPGA-built-in LED, which produces a light burst every time the i_TX_DV is set to '1'( for its very short amount of time). ]

Therefore, the UART-TX entity is triggered only the first time I pressed the button. Apparently when on FPGA for some reason, i_TX_DV is not set to '1' anymore, or is set to '0' just right after.

I am using the fpga Crosslink-NX Family 8MG289C from Lattice Semiconductor.