So I'm trying to understand how ARM7 processors work; I can't wrap my head around the MLA instruction.

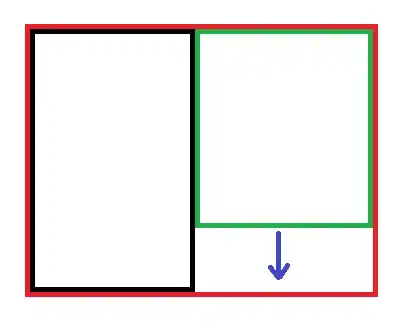

ARM7 register bank has only 2 outputs other than pc_read. How can it read Rm and Rs and Rn at the same time to perform a multiply-accumulate instruction?! (Rd:=Rm*Rs+Rn)

Could you walk me through the process of how it works step by step from fetch to writing back to Rs?