They are the same, the link you posted is the reference datasheet for IO APICs.

An IO APIC it's little more than a look-up table from the software perspective. So the specs never changed.

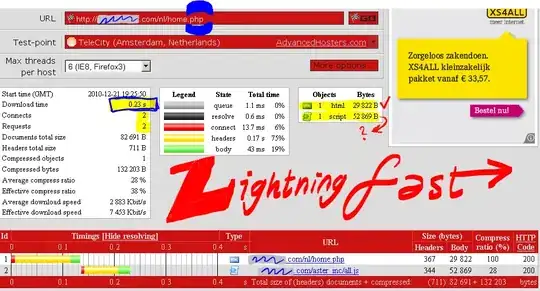

This picture in the Z8000 datasheet

is showing the same functionality as the IO APIC datasheet you linked.

Yes, the different naming is unfortunate but the IO APIC dates back to 1996 and a lot of engineers came and went at Intel meanwhile.

The register offsets match.

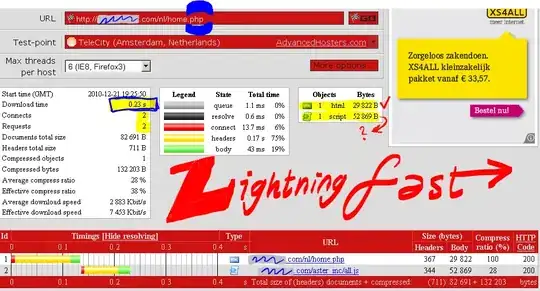

Anyway, the Z8000 datasheet describes the registers (I used a picture because I could copy-paste from the PDF):

The only new detail is the EOI register.

As brendan pointed out Intel updated the LAPIC interface (note the LAPIC, not the IO APIC interface) with the x2APIC specification.

This includes a Directed EOI feature where the OS configures the LAPIC not to send the EOI to any IO APIC. The OS will take care of signaling the EOI to the LAPIC and to the IO APIC of interest.

The Z8000 supports both modes: the LAPIC or the OS writing the EOI to the IO APIC.

The datasheet references the legacy mode where the LAPIC does the writing.

The original IO APIC used a dedicated bus for communication with the LAPIC (the APIC bus).

The software would signal the end of an interrupt through the EOI register in the LAPIC (note: not the IO APIC) and this, in turn, would signal the IO APIC.

Since the APIC bus disappeared, this IO APIC implementation has a dedicated MMIO register for EOI.

I wonder if this design allows for the IO APIC to be remapped when not using Directed EOI, I don't know how the LAPIC finds where the EOI register is if remapped.

Normally, as far as I understand it, older IO APICs have a dedicated bus (so they don't use MMIO registers for EOIs) while newer IO APICs are either in the uncore or behind a PCH or equivalent (so they use a virtual wire protocol over the uncore bus or DMI for EOIs).

This seems different, it's possible that the SoC translates the EOI message to the appropriate MMIO register by reading the configured base address for the IO APIC.

Actually, this may also apply to IO APICs behind a PCH and in the uncore, so that all recent IO APICs have an MMIO EOI register under the hood.