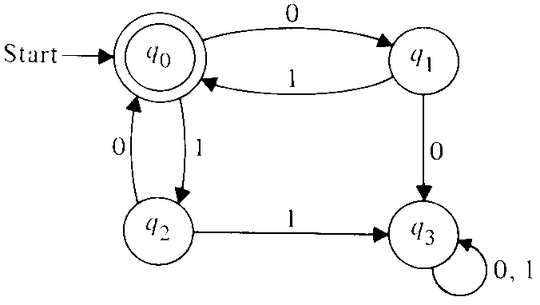

I don't understand how MIPS would implement the sll (shift left logical) instruction using the hardware present in its ALU as shown in the diagrams below. Would anyone be able to clarify what would be happening in it when it's executing an sll command? Thanks

Source: MIPS ALU

Source: MIPS ALU