I am not getting any response from the uut in the testbench. The module exp2_up_down_counter works ok without testbench, but gives output as xxxx when instantiated in the testbench.

Here is the main module of the up-down counter:

`timescale 1ns/1ps

module exp2_up_down_counter (input clk, reset, mode, output reg [3:0] count);

always @(posedge clk)

if (reset == 1)

count <= 0; // reset the counter if reset is high

else if (mode == 1)

count <= count + 1; // works as up counter if mode pin is high

else

count <= count - 1; // works as down counter if mode pin is low

endmodule

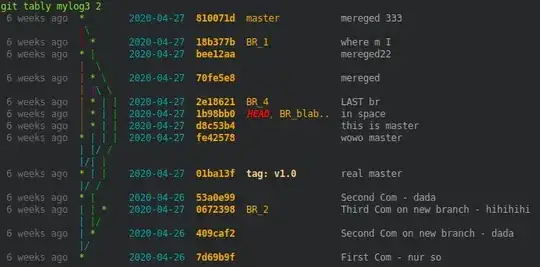

Simulation without testbench:

Testbench for up-down counter

`timescale 1ns/1ps

module exp2_up_down_counter_tb;

reg clk, reset, mode;

wire [3:0] count;

exp2_up_down_counter uut(.clk(clk), .reset(reset), .mode(mode), .count(count));

initial begin

clk = 1'b0;

end

always @(*) #5 clk <= ~clk;

initial begin

// initializing the inputs

reset = 1;

mode = 0;

#5;

reset = 0;

#10

mode = 1;

#5000 $finish;

end

endmodule

Simulation with testbench: