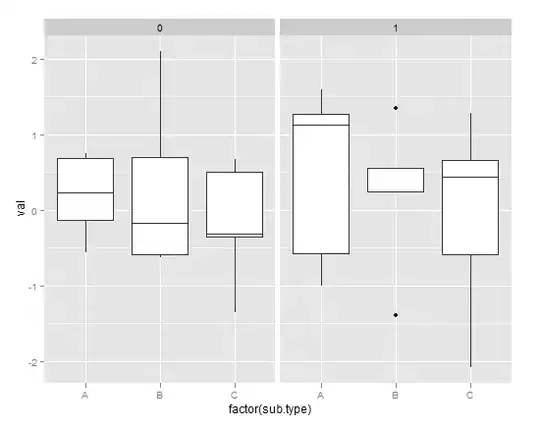

Consider the following digital logic circuit, which has multiple inputs and one output:

The logic circuit above can be represented in tree form:

This tree representation could then be used in a tree-based genetic programming framework to evolve the circuit. For example, this tree could be represented as a Lisp list (or (and A B) (not C)), which could then be used with the Little LISP genetic programming framework from John R. Koza's Genetic Programming textbook.

However, I now want to deal with digital logic circuits that have more than one output. For example, in the half-adder circuit below, there are two outputs S and C, each of which is affected by both inputs A and B.

(Image source: SICP by Abelson et al. Section 3.3.4 A Simulator for Digital Circuits. CC BY-SA 4.0)

How do I represent and evolve such a circuit in tree-based genetic programming? How do I represent the circuit above as a tree that could then be used to evolve the circuit using a tree-based genetic programming framework?