I'm doing a BCD counter that can count up/down depending on the input signals. This is the requirement:

This is my VHDL code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- main

entity BCDcounter is

port(

D_in: in std_logic_vector(3 downto 0);

enable_in, load_in, up_in, clr_in, clk_50hz: in std_logic;

C_out: out std_logic;

LED0: out std_logic_vector(0 to 6)

);

end BCDcounter;

architecture Behavioral of BCDcounter is

signal Q_temp: std_logic_vector(3 downto 0);

signal clk_1hz: std_logic;

component Clock_Divider is

port ( clk,reset: in std_logic;

clock_out: out std_logic);

end component;

component BCD_counter is

port(

D: in std_logic_vector(3 downto 0);

enable, load, up, clr, clk: in std_logic;

Q: std_logic_vector(3 downto 0);

Cout: out std_logic

);

end component;

component led IS

PORT ( input : IN STD_LOGIC_VECTOR(3 downto 0);

output : OUT STD_LOGIC_VECTOR(6 downto 0));

end component;

begin

stage0: Clock_Divider port map(clk_50hz, clr_in, clk_1hz);

stage1: BCD_counter port map(D_in, enable_in, load_in, up_in, clr_in, clk_1hz, Q_temp, C_out);

stage2: led port map(Q_temp, LED0);

end Behavioral;

-- 1-digit BCD counter

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity BCD_counter is

port(

D: in std_logic_vector(3 downto 0);

enable, load, up, clr, clk: in std_logic;

Q: std_logic_vector(3 downto 0);

Cout: out std_logic

);

end BCD_counter;

architecture bhv of BCDcounter is

signal temp: std_logic_vector(3 downto 0);

begin

process(enable, load, up, clr, clk)

begin

if clr = '0' then

temp <= "0000";

elsif enable = '0' then

temp <= "0000";

elsif load = '1' then -- load = 1, enable = 1

temp <= D;

elsif(rising_edge(clk)) then -- load = 0, enable = 1

if up = '1' then -- count up

if temp = "1001" then

temp <= "0000";

Cout <= '1';

else

temp <= temp + 1;

end if;

else -- count down

if temp = "0000" then

temp <= "1001";

Cout <= '1';

else

temp <= temp - 1;

end if;

end if;

end if;

end process;

Q <= temp;

end bhv;

-- Clock Divider from 50MHz to 1Hz

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.ALL;

entity Clock_Divider is

port ( clk,reset: in std_logic;

clock_out: out std_logic);

end Clock_Divider;

architecture behavioral of Clock_Divider is

signal count: integer:=1;

signal tmp : std_logic := '0';

begin

process(clk,reset)

begin

if(reset='1') then

count <= 1;

tmp <= '0';

elsif(clk'event and clk='1') then

count <= count+1;

if (count = 25000000) then

tmp <= NOT tmp;

count <= 1;

end if;

end if;

clock_out <= tmp;

end process;

end behavioral;

-- LED 7 segments

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY led IS

PORT ( input : IN STD_LOGIC_VECTOR(3 downto 0);

output : OUT STD_LOGIC_VECTOR(6 downto 0));

END led;

ARCHITECTURE behave OF led IS

BEGIN

PROCESS(input)

BEGIN

CASE input IS -- abcdefg

WHEN "0000" => output <= "0000001";

WHEN "0001" => output <= "1001111";

WHEN "0010" => output <= "0010010";

WHEN "0011" => output <= "0000110";

WHEN "0100" => output <= "1001100";

WHEN "0101" => output <= "0100100";

WHEN "0110" => output <= "0100000";

WHEN "0111" => output <= "0001111";

WHEN "1000" => output <= "0000000";

WHEN "1001" => output <= "0000100";

WHEN OTHERS => output <= "1111111";-- ALL OFF

END CASE;

END PROCESS;

END behave;

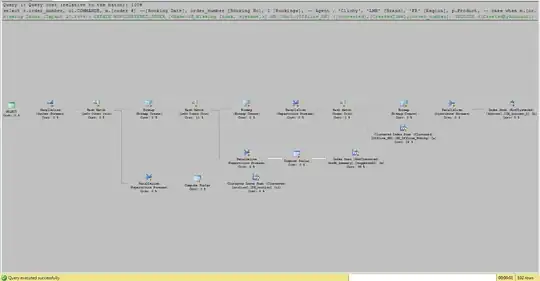

When compiling, I meet the error like this although I have already declared them above. Can anyone show me what problem with my code and how to fix this error? Thank you so much.