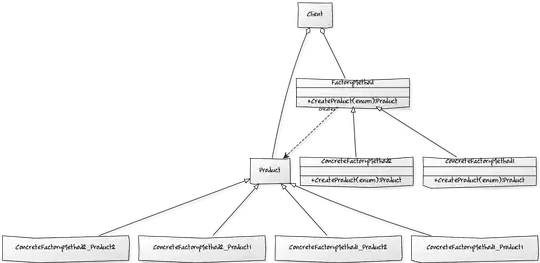

The diagram below is taken from ARMv8-A Programmer's Guide:

I am a bit confused by the highlighted entry type. Let me state my current understanding first (suppose the scenario of a stage 1 translation in EL3 with granule size 4KB).

In the first place, it seems that the name "entry" and "descriptor" is interchangeable in this context.

Then, according to ARM ARM doc (e.g. Figure D5-6), it seems that there are 3 types of valid descriptors:

- D_Table descriptor, which is an entry pointing to the next level translation table. Reaching this type of descriptor means that the translation walk is not complete yet.

- D_Block descriptor, which is an entry pointing to a memory "region" which is bigger than the granule size ("page"). This is one of the two cases where a translation walk completes.

- D_Page descriptor, which points to a memory "page" of the granule size. This is the second case where a translation walk completes.

There are also several constraints (w.r.t valid descriptors), namely:

- L0 table can only contain D_Table descriptors, no other two types (D_Block, D_Page).

- L3 can only contain D_Page descriptors.

- D_Block can only appear in L1/L2 translation tables.

So back to the diagram above, I don't understand why there is another Table entry for L1 and L2? Because the 1st line in the diagram depicts table descriptor for L0/L1/L2 already. Then, even if this is another table descriptor type, why the middle content is marked as "Output block address" (instead of "Next level table address")?