I see this image in ARM's AHB spec. This is basically an example of how we can use the AHB fabric to connect with narrower slave. Here I am not able to understand the usage of haddr[2] as a mux select. How will this bit help us in figuring out if we need to select upper or lower half of the data bus. Please help me in understanding this .

-

1it is a wrong forum to ask this question. The question has nothing to do with verilogs. Try https://electronics.stackexchange.com. – Serge Jul 20 '21 at 10:35

1 Answers

Define: Quadword=QW=a 64-bit word.

Define: Dword=DW=a 32-bit word.

Define: Byte= an 8-bit word.

The address bus HADDR[] refers to bytes.

Address 0 refers to byte 0, address 1 refers to byte 1, ...

The memory is 64-bit, therefore the 3 least significant bits of the address have no meaning to a 64-bit wide memory.

Any address from 0-7 will produce the first QW from the memory.

Any address from 8-15 will produce the 2nd QW from the memory.

...

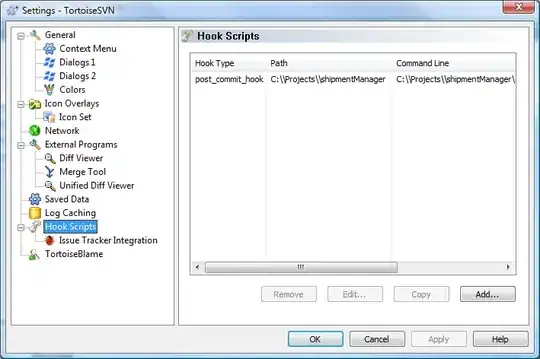

Example of how to read out the memory to facilitate the conversion from 64->32-bit.

First, drive the memory with address 0 during the first clock cycle, the memory will present the first QW, address[2] will be 0 so the low DW (data[31:0]) of the first QW will get selected by the mux.

Second, drive the memory with address 4 during the second clock cycle, the memory will continue to present the first QW, address[2] will be 1 so the high DW (data[63:32]) of the first QW will get selected by the mux.

Third, drive the memory with address 8 during the third clock cycle, the memory will present the second QW, address[2] will be 0 so the low DW (data[31:0]) of the second QW will get selected by the mux.

Repeat the pattern incrementing the address by 4 each clock to read the 64 bit memory and convert to 32-bit using the circuit shown.

- 1,572

- 2

- 10

- 21