I am new to Verilog language and want to do some practices to get familiar with it. And I encountered this problem on HDLbits: DFF8ar

This problem asks me to create 8 D flip-flops with active-high asynchronous reset. I use a case statement to handle the areset signal:

module top_module (

input clk,

input areset, // active high asynchronous reset

input [7:0] d,

output reg[7:0] q

);

always @(posedge clk or posedge areset) begin

case (areset)

1'b1: q <= 8'b0;

default: q <= d;

endcase

end

endmodule

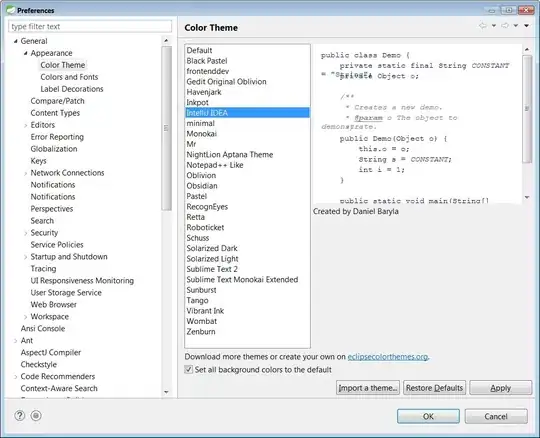

And to my surprise, the circuit it generated ignores the clk signal:

But, if I switch the case statement to an if-else statement, the result will be correct:

always @(posedge clk or posedge areset) begin

if (areset)

q <= 8'b0;

else q <= d;

end

I don't know the reason behind it even after doing some research. Does if-else statements and case statements have some fundamental difference? Any help is appreciated!