I'm trying to write a code in vhdl to create a 16 to 1 mux using 2 to 1 mux. I actually thought that to do this we may need 15 two to one multiplexers and by wiring them together and using structural model I wrote the code below. First I wrote a 2 to 1 mux:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity MUX_2_1 is

port (

w0 , w1 : IN STD_LOGIC;

SELECT_I: IN std_logic;

DATA_O: out std_logic

);

end MUX_2_1;

architecture MUX_2_1_arch of MUX_2_1 is

--

begin

--

WITH SELECT_I SELECT

DATA_O <= w0 WHEN '0',

w1 WHEN '1',

'X' when others;

--

end MUX_2_1_arch;

and made a package from it, just to use it simple and easy:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

PACKAGE mux2to1_package IS

COMPONENT mux2to1

PORT (w0, w1: IN STD_LOGIC ;

SELECT_I: IN std_logic;

DATA_O: out std_logic ) ;

END COMPONENT ;

END mux2to1_package ;

and then my 16 to 1 mux looks like this:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

USE work.mux2to1_package.all ;

ENTITY mux16to1 IS

PORT (w : IN STD_LOGIC_VECTOR(15 DOWNTO 0) ;

s : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;

f : OUT STD_LOGIC ) ;

END mux16to1 ;

ARCHITECTURE Structure OF mux16to1 IS

SIGNAL im : STD_LOGIC_VECTOR(7 DOWNTO 0) ;

SIGNAL q : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL p : STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

Mux1: mux2to1 PORT MAP ( w(0), w(1), s(0), im(0)) ;

Mux2: mux2to1 PORT MAP ( w(2), w(3), s(0), im(1)) ;

Mux3: mux2to1 PORT MAP ( w(4), w(5), s(0), im(2)) ;

Mux4: mux2to1 PORT MAP ( w(6), w(7), s(0), im(3)) ;

Mux5: mux2to1 PORT MAP ( w(8), w(9), s(0), im(4)) ;

MUX6: mux2to1 PORT MAP ( w(10), w(11), s(0), im(5));

Mux7: mux2to1 PORT MAP ( w(12), w(13), s(0), im(6)) ;

Mux8: mux2to1 PORT MAP ( w(14), w(15), s(0), im(7)) ;

Mux9: mux2to1 PORT MAP ( im(0), im(1), s(1), q(0)) ;

Mux10: mux2to1 PORT MAP ( im(2), im(3), s(1), q(1)) ;

Mux11: mux2to1 PORT MAP ( im(4), im(5), s(1), q(2)) ;

Mux12: mux2to1 PORT MAP ( im(6), im(7), s(1), q(3)) ;

Mux13: mux2to1 PORT MAP ( q(0), q(1), s(2), p(0)) ;

Mux14: mux2to1 PORT MAP ( q(2), q(3), s(2), p(1)) ;

Mux15: mux2to1 PORT MAP ( p(0), p(1), s(3), f) ;

END Structure ;

and also my testbench is:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

USE work.mux2to1_package.all ;

ENTITY Mux_test IS

END Mux_test;

ARCHITECTURE test OF Mux_test IS

COMPONENT mux16to1 PORT(w : IN STD_LOGIC_VECTOR(15 DOWNTO 0) ;

s : IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;

f : OUT STD_LOGIC ) ;

END COMPONENT;

SIGNAL wi : STD_LOGIC_VECTOR(15 DOWNTO 0) ;

SIGNAL selecting : STD_LOGIC_VECTOR(3 DOWNTO 0) ;

SIGNAL fi : STD_LOGIC ;

BEGIN

a1: mux16to1 PORT MAP(wi , selecting , fi);

wi<= "0101110010001010" , "1001000101010101" after 100 ns;

selecting <= "0011" , "1010" after 20 ns , "1110" after 40 ns, "1100" after 60 ns , "0101" after 80 ns,

"0011" after 100 ns , "1010" after 120 ns , "1110" after 140 ns, "1100" after 160 ns , "0101" after 180 ns;

END ARCHITECTURE;

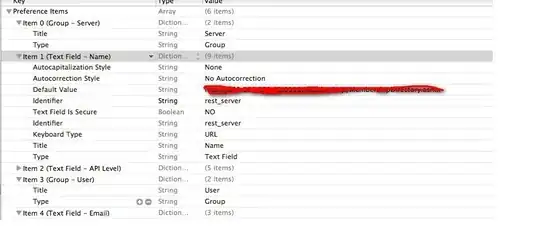

my simulation:

But when I try to simulate this nothing shows in my output. I'm thinking that maybe that's because I wrote my code in concurrent part and signals im and q and p are not initialized yet so I tried using default values "00000000" for im and "0000" for q and "00" for p when I was declaring the signals, but then I got bunch of errors saying "Instance mux2to1 is unbound" in simulation and nothing actually changed.

Any idea what is the problem??

Also I think there is something wrong with my select input logically. but I don't understand how i should use the select to be correct for this problem. I would appreciate if anyone can help me with my problem.