Here is my code, the professor say module format cannot be changed. And the homework also require only the input can be load when rst_n=1, and the output should be 0 when rst_n = 0. But in test bench all my result always is 00000000, zero is 1, cout is 0, overflow is 1, what's the problem with my code?

I thought the problem maybe are here, but I have no idea how to edit it.

(I use //problem to mark to line in code below)

cout = out; //problem

result = results; //problem

result <= 32'b0; //problem

`timescale 1ns/1ps

module ALU_1bit(

input src1, //1 bit source 1 (input)

input src2, //1 bit source 2 (input)

input Ainvert, //1 bit A_invert (input)

input Binvert, //1 bit B_invert (input)

input Cin, //1 bit carry in (input)

input [2-1:0] operation, //2 bit operation (input)

output reg result, //1 bit result (output)

output reg cout //1 bit carry out (output)

);

/* Write your code HERE */

reg temp1;

reg temp2;

reg temp3;

reg temp4;

reg temp5;

always@(src1 or src2 or Ainvert or Binvert or Cin or operation)

begin

case (Ainvert)

1'b0: temp1 = src1; // 0

1'b1: temp1 = ~src1; // 1

endcase

//$display("temp1 %d", temp1);

case (Binvert)

1'b0: temp2 = src2; // 0

1'b1: temp2 = ~src2; // 1

endcase

//$display("temp2 %d", temp2);

temp3 = temp1 & temp2;

temp4 = temp1 | temp2;

{cout, temp5} = temp1 + temp2 + Cin;

//$display("temp3 %d", temp3);

//$display("temp4 %d", temp4);

//$display("temp5 %d", temp5);

case (operation)

2'b00: result = temp3; // AND

2'b01: result = temp4; // OR

2'b10: result = temp5; // addition

2'b11: result = temp5; // addition

endcase

end

endmodule

module alu(

input rst_n, // negative reset (input)

input [32-1:0] src1, // 32 bits source 1 (input)

input [32-1:0] src2, // 32 bits source 2 (input)

input [ 4-1:0] ALU_control, // 4 bits ALU control input (input)

output reg [32-1:0] result, // 32 bits result (output)

output reg zero, // 1 bit when the output is 0, zero must be set (output)

output reg cout, // 1 bit carry out (output)

output reg overflow // 1 bit overflow (output)

);

/* only below can be edit */

wire [32-1:0]results;

wire out;

wire carryout0, carryout1, carryout2, carryout3, carryout4, carryout5, carryout6, carryout7, carryout8, carryout9, carryout10, carryout11, carryout12, carryout13, carryout14, carryout15, carryout16, carryout17, carryout18, carryout19, carryout20, carryout21, carryout22, carryout23, carryout24, carryout25, carryout26, carryout27, carryout28, carryout29, carryout30;

ALU_1bit UUT0(src1[0], src2[0], ALU_control[3], ALU_control[2], ALU_control[2], ALU_control[1:0], results[0], carry0);

ALU_1bit UUT1(src1[1], src2[1], ALU_control[3], ALU_control[2], carry0, ALU_control[1:0], results[1], carry1);

ALU_1bit UUT2(src1[2], src2[2], ALU_control[3], ALU_control[2], carry1, ALU_control[1:0], results[2], carry2);

ALU_1bit UUT3(src1[3], src2[3], ALU_control[3], ALU_control[2], carry2, ALU_control[1:0], results[3], carry3);

ALU_1bit UUT4(src1[4], src2[4], ALU_control[3], ALU_control[2], carry3, ALU_control[1:0], results[4], carry4);

ALU_1bit UUT5(src1[5], src2[5], ALU_control[3], ALU_control[2], carry4, ALU_control[1:0], results[5], carry5);

ALU_1bit UUT6(src1[6], src2[6], ALU_control[3], ALU_control[2], carry5, ALU_control[1:0], results[6], carry6);

ALU_1bit UUT7(src1[7], src2[7], ALU_control[3], ALU_control[2], carry6, ALU_control[1:0], results[7], carry7);

ALU_1bit UUT8(src1[8], src2[8], ALU_control[3], ALU_control[2], carry7, ALU_control[1:0], results[8], carry8);

ALU_1bit UUT9(src1[9], src2[9], ALU_control[3], ALU_control[2], carry8, ALU_control[1:0], results[9], carry9);

ALU_1bit UUT10(src1[10], src2[10], ALU_control[3], ALU_control[2], carry9, ALU_control[1:0], results[10], carry10);

ALU_1bit UUT11(src1[11], src2[11], ALU_control[3], ALU_control[2], carry10, ALU_control[1:0], results[11], carry11);

ALU_1bit UUT12(src1[12], src2[12], ALU_control[3], ALU_control[2], carry11, ALU_control[1:0], results[12], carry12);

ALU_1bit UUT13(src1[13], src2[13], ALU_control[3], ALU_control[2], carry12, ALU_control[1:0], results[13], carry13);

ALU_1bit UUT14(src1[14], src2[14], ALU_control[3], ALU_control[2], carry13, ALU_control[1:0], results[14], carry14);

ALU_1bit UUT15(src1[15], src2[15], ALU_control[3], ALU_control[2], carry14, ALU_control[1:0], results[15], carry15);

ALU_1bit UUT16(src1[16], src2[16], ALU_control[3], ALU_control[2], carry15, ALU_control[1:0], results[16], carry16);

ALU_1bit UUT17(src1[17], src2[17], ALU_control[3], ALU_control[2], carry16, ALU_control[1:0], results[17], carry17);

ALU_1bit UUT18(src1[18], src2[18], ALU_control[3], ALU_control[2], carry17, ALU_control[1:0], results[18], carry18);

ALU_1bit UUT19(src1[19], src2[19], ALU_control[3], ALU_control[2], carry18, ALU_control[1:0], results[19], carry19);

ALU_1bit UUT20(src1[20], src2[20], ALU_control[3], ALU_control[2], carry19, ALU_control[1:0], results[20], carry20);

ALU_1bit UUT21(src1[21], src2[21], ALU_control[3], ALU_control[2], carry20, ALU_control[1:0], results[21], carry21);

ALU_1bit UUT22(src1[22], src2[22], ALU_control[3], ALU_control[2], carry21, ALU_control[1:0], results[22], carry22);

ALU_1bit UUT23(src1[23], src2[23], ALU_control[3], ALU_control[2], carry22, ALU_control[1:0], results[23], carry23);

ALU_1bit UUT24(src1[24], src2[24], ALU_control[3], ALU_control[2], carry23, ALU_control[1:0], results[24], carry24);

ALU_1bit UUT25(src1[25], src2[25], ALU_control[3], ALU_control[2], carry24, ALU_control[1:0], results[25], carry25);

ALU_1bit UUT26(src1[26], src2[26], ALU_control[3], ALU_control[2], carry25, ALU_control[1:0], results[26], carry26);

ALU_1bit UUT27(src1[27], src2[27], ALU_control[3], ALU_control[2], carry26, ALU_control[1:0], results[27], carry27);

ALU_1bit UUT28(src1[28], src2[28], ALU_control[3], ALU_control[2], carry27, ALU_control[1:0], results[28], carry28);

ALU_1bit UUT29(src1[29], src2[29], ALU_control[3], ALU_control[2], carry28, ALU_control[1:0], results[29], carry29);

ALU_1bit UUT30(src1[30], src2[30], ALU_control[3], ALU_control[2], carry29, ALU_control[1:0], results[30], carry30);

ALU_1bit UUT31(src1[31], src2[31], ALU_control[3], ALU_control[2], carry30, ALU_control[1:0], results[31], out);

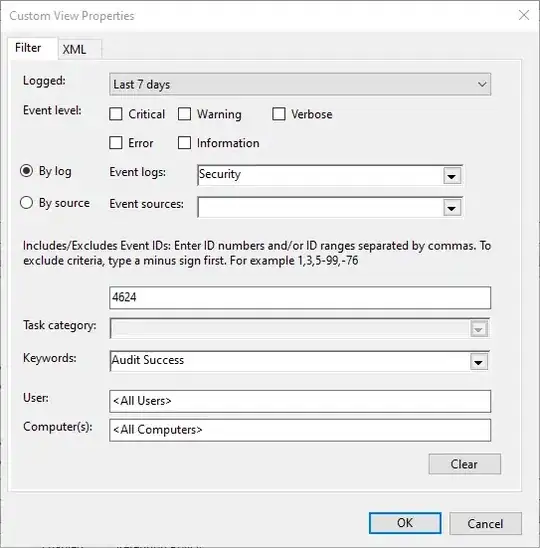

always@(posedge rst_n) begin

cout = out; //problem

result = results; //problem

zero = ~(|result);

overflow = result[31] ^ cout;

end

always@(negedge rst_n) begin

result <= 32'b0; //problem

zero = 0;

overflow = 0;

end

endmodule

testbench

`timescale 1ns/1ps

module testbench;

parameter PATTERN_NUMBER = 6'd30;

reg clk;

reg rst_n;

reg [32-1:0] src1_in;

reg [32-1:0] src2_in;

reg [4-1:0] operation_in;

reg [8-1:0] mem_src1 [0:(PATTERN_NUMBER*4-1)];

reg [8-1:0] mem_src2 [0:(PATTERN_NUMBER*4-1)];

reg [8-1:0] mem_opcode [0:(PATTERN_NUMBER-1)];

reg [8-1:0] mem_result [0:(PATTERN_NUMBER*4-1)];

reg [8-1:0] mem_zcv [0:(PATTERN_NUMBER-1)];

reg [6-1:0] pattern_count;

reg start_check;

reg [6-1:0] error_count;

reg [6-1:0] correct_count;

reg [6-1:0] error_count_tmp;

wire [32-1:0] result_out;

wire zero_out;

wire cout_out;

wire overflow_out;

wire [3-1:0] zcv_out;

wire [32-1:0] result_correct;

wire [3-1:0] zcv_correct;

wire [4-1:0] opcode_tmp;

assign zcv_out = {zero_out, cout_out, overflow_out};

assign opcode_tmp = mem_opcode[pattern_count];

assign result_correct = {mem_result[4*(pattern_count-1) + 5'd3],

mem_result[4*(pattern_count-1) + 5'd2],

mem_result[4*(pattern_count-1) + 5'd1],

mem_result[4*(pattern_count-1) + 5'd0]};

assign zcv_correct = mem_zcv[pattern_count-1];

initial begin

clk = 1'b0;

rst_n = 1'b0;

src1_in = 32'd0;

src2_in = 32'd0;

operation_in = 4'h0;

start_check = 1'd0;

error_count = 6'd0;

correct_count = 6'd0;

error_count_tmp = 6'd0;

pattern_count = 6'd0;

$readmemh("src1.txt", mem_src1);

$readmemh("src2.txt", mem_src2);

$readmemh("op.txt", mem_opcode);

$readmemh("result.txt", mem_result);

$readmemh("zcv.txt", mem_zcv);

#100 rst_n = 1'b1;

start_check = 1'd1;

//$dumpfile("alu.vcd");

//$dumpvars(0,testbench);

end

always #5 clk = ~clk;

alu alu(

.rst_n(rst_n),

.src1(src1_in),

.src2(src2_in),

.ALU_control(operation_in),

.result(result_out),

.zero(zero_out),

.cout(cout_out),

.overflow(overflow_out)

);

always@(posedge clk) begin

if(pattern_count == (PATTERN_NUMBER+1)) begin

if(error_count == 6'd0) begin

$display("* Congratulation! All data are correct! *");

$display("***************************************************");

$display("Correct Count: %2d", correct_count );

end

else begin

end

$finish;

end

else if(rst_n) begin

src1_in <= {mem_src1[4*pattern_count + 6'd3],

mem_src1[4*pattern_count + 6'd2],

mem_src1[4*pattern_count + 6'd1],

mem_src1[4*pattern_count + 6'd0]};

src2_in <= {mem_src2[4*pattern_count + 6'd3],

mem_src2[4*pattern_count + 6'd2],

mem_src2[4*pattern_count + 6'd1],

mem_src2[4*pattern_count + 6'd0]};

operation_in <= opcode_tmp;

pattern_count <= pattern_count + 6'd1;

end

end

always@(posedge clk) begin

if(start_check) begin

if(pattern_count==0) begin

$display("***************************************************");

$display("* PATTERN RESULT TABLE *");

$display("***************************************************");

$display("* PATTERN * Result * ZCV *");

$display("***************************************************");

end

else if(pattern_count < (PATTERN_NUMBER+1)) begin

if(result_out == result_correct) begin

if(zcv_out != zcv_correct) begin

$display("* No.%2d error! *",pattern_count);

$display("* Correct result: %h Correct ZCV: %b *",result_correct, zcv_correct[3-1:0]);

$display("* Your result: %h Your ZCV: %b *",result_out, zcv_out);

$display("***************************************************");

error_count <= error_count + 6'd1;

end

else begin

correct_count <= correct_count + 6'd1;

end

end

else begin

$display("* No.%2d error! *",pattern_count);

$display("* Correct result: %h Correct ZCV: %b *",result_correct, zcv_correct[3-1:0]);

$display("* Your result: %h Your ZCV: %b *",result_out, zcv_out);

$display("***************************************************");

error_count <= error_count + 6'd1;

end

end

end

end

endmodule

result error

***************************************************

* PATTERN RESULT TABLE *

***************************************************

* PATTERN * Result * ZCV *

***************************************************

* No. 1 error! *

* Correct result: eeeeeeee Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 3 error! *

* Correct result: 9bf5fea6 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 4 error! *

* Correct result: 00000000 Correct ZCV: 110 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 5 error! *

* Correct result: fffffffe Correct ZCV: 001 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 6 error! *

* Correct result: 70459a76 Correct ZCV: 011 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 7 error! *

* Correct result: 7530eca9 Correct ZCV: 010 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 8 error! *

* Correct result: 00000001 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No. 9 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.11 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.12 error! *

* Correct result: 00000000 Correct ZCV: 110 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.13 error! *

* Correct result: 00000000 Correct ZCV: 110 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.14 error! *

* Correct result: 00000001 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.15 error! *

* Correct result: 00000000 Correct ZCV: 110 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.16 error! *

* Correct result: 000000ff Correct ZCV: 010 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.18 error! *

* Correct result: 00000001 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.21 error! *

* Correct result: 00000001 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.22 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.23 error! *

* Correct result: 12345678 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.24 error! *

* Correct result: 02244220 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.26 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.27 error! *

* Correct result: 97755779 Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.28 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************

* No.30 error! *

* Correct result: ffffffff Correct ZCV: 000 *

* Your result: 00000000 Your ZCV: 100 *

***************************************************