I want to write a module in Verilog that outputs the same 32-bit input at positive clock edge. However, I have some trouble with the loop conditions.

Asked

Active

Viewed 1,000 times

-1

-

1in verilog there is no `+=` operator. you would need `i = i+1` instead. Or you can switch to system verilog. Also you have a bunch of other syntactic errors in port declaration. – Serge Oct 19 '20 at 11:07

1 Answers

2

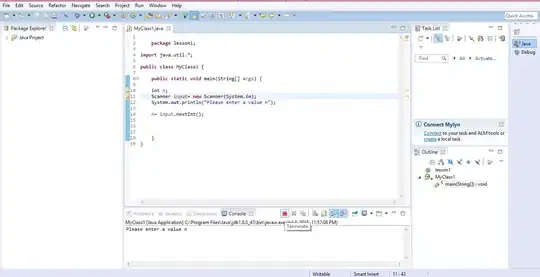

module if_id (

input clk

,input [31:0] in

,output reg [31:0] out

);

always@(posedge clk)

out <= in;

endmodule

you don't need to write looping code if your intention is to register a 32bit value . But if u need to write it in array mode u need to use genvar variable in your code. By the way int isn't supported in verilog variants . migrate to System-verilog for more number of data types.

Rama Krishna Meda

- 363

- 2

- 8

-

-

1Please go through `genvar` variable in verilog u will get basic understanding of `for` loop variable usage context in hardware languages – Rama Krishna Meda Oct 19 '20 at 15:32