(I am learning the Cortex-M microcontroller and can't help compare it to the x86 cpu.)

With x86, for a fault, such as page fault, the instruction that caused/triggered the fault will be executed again after the fault has been handled.

But with ARM NVIC, I didn't see such mechanism. The NVIC hardware just automatically place the R0-R3, R12, PC, LR, SP xPSR onto the stack at the ISR entry (with no interference from programmer). And restore this register context from stack at the ISR exit. Based on my debugging, after the restore, the PC register will still point to the address of the interrupted instruction.

I think an interrupt can only happen at the boundary of a cycle (correct me if I am wrong). I am not sure if below 2 guesses hold:

For a single-cycle instruction, that interrupted instruction will be executed again since the PC still points to it.

For a multi-cycle instruction, the remaining cycles of the interrupted instruction should be continued.

I guess these 2 scenarios should be guaranteed by the micro-code that implement the instructions.

So my questions are:

Does ARM NVIC has a mechanism like x86 to re-execute the instruction that caused fault?

Does the interrupted instruction get continued like the 2 scenarios above?

ADD 1 -- 9:31 PM 10/6/2020

Thanks to domen's reminding.

I checked some materials on exceptional control flows, exceptions are usually classified as:

- interrupt (happens asynchronously, handled after current instruction finishes, handler returns to next instruction.)

- trap (happens synchronously, intentionally triggered by current instruction, handler returns to next instruction.)

- fault (happens asynchronously, relevant to current instruction or not, handler returns to current instruction.)

- abort (happens asynchronously, relevant to current instruction or not, handler never returns to application but to a special abort routine.)

I checked the ARMv7-M Arch Ref Manual. In section B1.5.6 Exception Entry Behavior, I found a pseudo-code for determining the return address:

So for different exception types, different return addresses can be returned . Both ThisInstrAddr and NextInstrAddr are possible.

I think there should be a little correction to the previous 2 scenarios. That is, the PC value automatically pushed onto the stack by the hardware is the ReturnAddress. And it can be ThisInstrAddr or NextInstrAddr.

ADD 2 -- 10:32 PM 10/6/2020

Thanks to old_timer. Yes I did mix up the fault and interrupt a bit. Fault doesn't go through the NVIC, interrupt does.

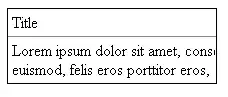

And below is a the priority list of internal exception/fault and external interrupts. (quoted from the The Designer's Guide to Cortex-M Processor Family 2nd edition)