I have an ice40 that drives the clock and data inputs of an ASIC.

The ice40 drives the ASIC's clock with the same clock that drives the ice40's internal logic. The problem is that the rising clock triggers the ice40's internal logic and changes the ice40's data outputs a few nanoseconds before the rising clock reaches the ASIC, and therefore the ASIC observes the wrong data at its rising clock.

I've solved this issue by using an inverter chain to delay the ice40's internal clock without delaying the clock driving the ASIC. That way, the rising clock reaches the ASIC before the ice40's data outputs change. But that raises a few questions:

Is my strategy -- using an inverter chain to delay the ice40 internal clock -- a good strategy?

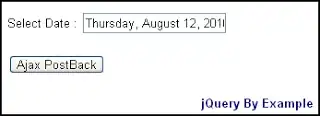

To diagnose the problem, I used Lattice's iCEcube2 to analyze the min/max delays between the internal clock and output pins:

Notice that the asic_dataX delays are shorter than the clk_out delay, indicating the problem.

Is there a way to get this information from yosys/nextpnr?

Thank you for any insight!