I have an FPGA which accepts an 8-bit address and data bus (one bus is used for both) from two microcontrollers.

Using a 2:1 multiplexer, my FPGA only selects one device's inputs at a time (address and data) and the selection is based on an external signal to the FPGA.

I also have a separate decoder and register module which the microcontroller reads and writes to. How do I link the bidirectional output signal from my multiplexer to the decoder/register bidirectional input module at the higher level using the port map assignment?

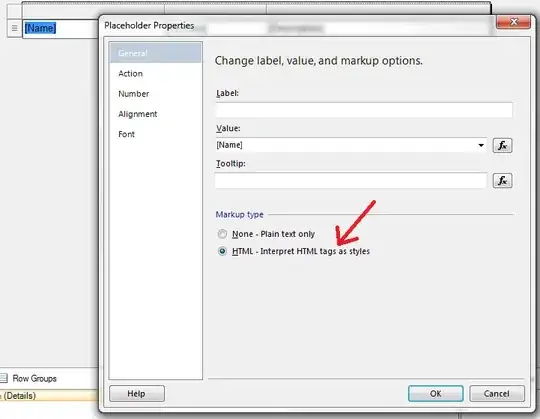

Using a std_logic_vector(7..0), it will not work as I get an error "this signal is connected to multiple drivers". I think I need to tri-state the two, but I'm not sure. Looking at the image below, the green circle is what I'm trying to glue together.