I'm trying to wrap my head around data paths and how it works in MIPS programming. A part of understating it, is understanding the ALU Opcodes that essentially tell the ALU which operations to carry out. For example, if we implement the basic AND, OR, ADD, SUB, NAND and NOR functions, we get a basic ALU Opcode distribution, i.e. AND is 00, OR is 01, ADD is 10, SUB is 10, NAND is 10 and NOR is 01. But I'm not sure I understand why the ALU Opcode for sw and lw are 00?

Asked

Active

Viewed 2,158 times

1

Peter Cordes

- 328,167

- 45

- 605

- 847

Ski Mask

- 351

- 1

- 2

- 14

-

1Where do you get this information about "ALU Opcode" for `lw` and `sw` from? – EOF Feb 21 '20 at 20:50

-

@EOF I got them from my lecture slides, but they don't have any explanation which is why I wasn't sure why there answer is 00. – Ski Mask Feb 21 '20 at 21:01

-

The format for (reg-reg) ALU instructions (R-Type encoding) in MIPS is `6 bit opcode, 5 bit rs, 5 bit rt, 5 bit rd, 5 bit SHAMT, 6 bit ALUop`. The format for `sw` and `lw` with a general register base (I-type), is `6 bit opcode, 5 bit rs, 5 bit rt, 16 bit immediate`. *Where* do you see an ALUop in the load/store instructions? – EOF Feb 21 '20 at 21:07

-

You are correct but if we have OR which is an R-Type, then the opcode is indeed 000000 however the ALU Opcode, when using a 2 bit signal, is 01. Additionally, in our sheet it says that the last 6 bits for R-Type is called the function and not ALUop. – Ski Mask Feb 21 '20 at 21:15

-

There are two possibilities: 1) You have misunderstood your lecturers diagrams, but since you have not posted them here, we cannot diagnose the origin of your misunderstanding. 2) Your lecturer has made an error on their diagrams, but since you have not posted them here... – EOF Feb 21 '20 at 21:19

-

I just added them. Originally in German, most of the stuff is in English so it shouldn't be a problem. – Ski Mask Feb 21 '20 at 21:22

-

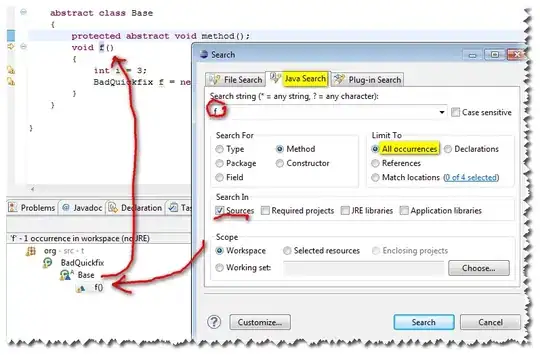

2I can't help but feel that this may not be everything required to follow your thoughts. Either way, you may notice that R-type instructions control the ALU via the last 6 bits of the instruction (see Instruction[5-0] in the bottom of the image), while `lw` and `sw` *definitely do not control the ALU that way, because these bits are immediate going into the ALU as an operand (Instruction[15-0])*. Rather, the ALUop from the "Control" component is a 2-bit selector for a mux deciding to use either the "function"-field in the Instruction, or override directly for some "opcode"s. – EOF Feb 21 '20 at 21:29

1 Answers

4

On MIPS, there is only one addressing mode: base + displacement.

In load and store instructions, the ALU performs this address computation, which is done using addition. Thus, the ALU performs the addition in: register + sign-extended immediate, which forms the address sent to the data memory.

Erik Eidt

- 23,049

- 2

- 29

- 53

-

But isn't the OP code for addition (ALU is 2 bits) 10? So if we are performing addition, shouldn't the OP code for lw and sw be 10? – Ski Mask Feb 21 '20 at 20:35

-

2The ALUOp is 00 (2-bits) and the ALU control is 010 (3-bits): addition. It gets translated from 00 to 010 by the ALU Control. I believe that you are confusing ALUOp and ALUControl -- but some slides & texts do this as well. Some texts describe the ALU control as 4-bits as well. (Btw, these are internal details of the processor implementation, so different values could be used without the program noticing.) – Erik Eidt Feb 21 '20 at 21:33

-

2The main Control provides 00 as ALUOp from `addi`, `lw` and `sw`, and that tells the ALU Control output the code for addition to the ALU. The main Control provides 01 as ALUOp for branches, which makes the ALU Control output the code for subtraction to the ALU. For the others, the main Control outputs 1x, which tells the ALU Control to look up the proper operation from the func[5:0] bits. – Erik Eidt Feb 21 '20 at 21:41