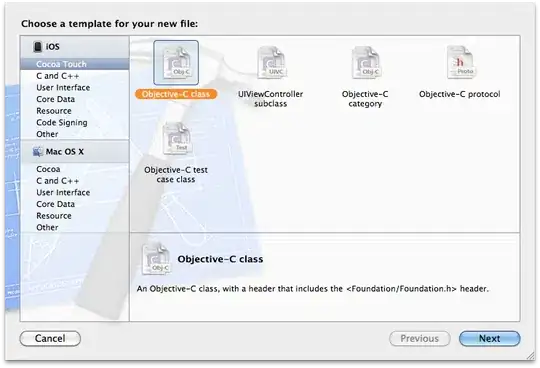

I want to write a behavioral verilog code for a FF with the following characteristics as shown in the picture.

module DFF ( D, CK, RN, Q );

input D, CK, RN;

output reg Q;

always @ (posedge CK)

begin

if ( RN==1'b0 )

Q <= RN ;

if ( RN==1'b1 )

Q <= D ;

if RN

I DONT KNOW WHAT TO WRITE HERE

end

);

endmodule