I have been trying to initialize my output LEDR [3:0] to all 0. However, LEDR keeps being XXXX in my waveform timing diagram. I have tried using initial block, but it doesn't work. (My IDE is Quartus Prime)

Here is my code

module synasyn_counter(SW,LEDR,PLoad,CLK);

parameter n=16;

input CLK,PLoad;

input [3:0] SW;

output reg [3:0] LEDR;

initial

begin

LEDR=0;

end

always @(negedge PLoad or negedge CLK)

begin

if (PLoad==0) LEDR<=SW;

else

begin

if (LEDR==n-1) LEDR<=0;

else LEDR<=LEDR+1;

end

end

endmodule

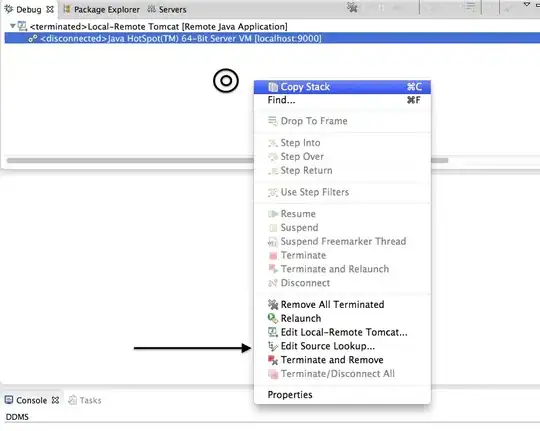

And this is my result: