In NEON inline assembly, after conversion from Signed int32 to Float the number is different.

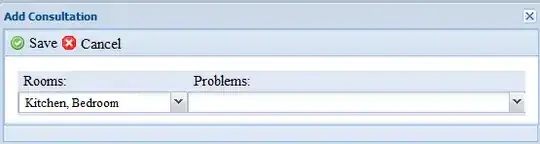

Here the output for Float and Signed int32 is printed:

It differs randomly (not only for each even number). There is only conversion (no any other operation) between save as sint32 and as float.

How to avoid it? Thanks