I'm learning VHDL at university and we use Xilinx. The professor told us to write a simple 8:1 multiplexer with multiple architecture implementations: structural (using hierarchical design with two 4:1 mux and one 2:1 mux), behavioral (with if-then-else and with case statement) and data flow (with when-else and with-select).

So, I have my 8:1 mux with 5 different architectures in the same VHDL file. Now I need to synthesize each architecture in order to compare the number of IO, the number of BELs and the maximum frequency.

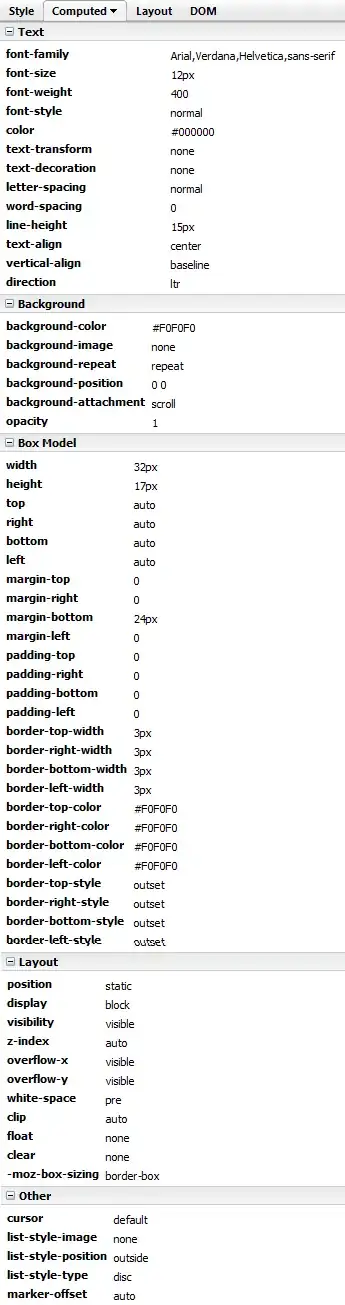

The problem is that I always get the same result, no matter the implementation I choose. I'm sure that I'm making a mistake somewhere in the synthesis process, my hierarchy looks like the one in the attached picture.

Do I have to write something in the file to tell the synthesizer which architecture to use like I've done in the testbench? This is a screenshot of my architecture: