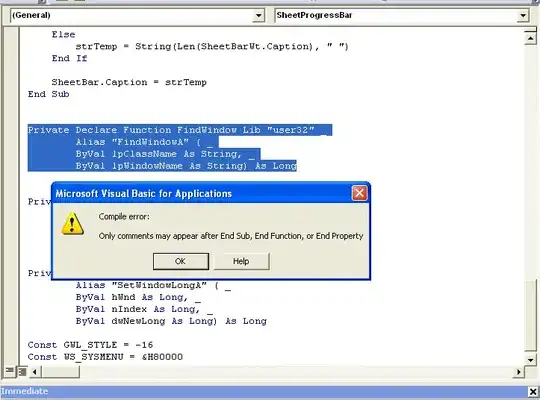

I have created my truth table and drawn from this a boolean expression (f = B'A' + CA' + DC' + DB + D'CB') which I have then attempted to convert into a circuit using Quartus.

I am new to digital logic and I need some help from someone wit experience who can tell me if what I have attempted looks correct.

I am unable to compile the circuit as I don't have 'device support installed'. If anyone could point me in the right direction for how to obtain that, that would be greatly appreciated.

This is the circuit I created based on the boolean expression.

This is my truth table. The circuit corresponds to the f column