I'm having some synthesis issues using 7 series GTX transceiver wizard in my project. I designed a basic custom protocol and a top level wrapper. In behavioral everything works just fine, but when synthesizing project the data bus attached to gt0_txdata_in[15:0] it's not properly rendered thus forcing unknown "X" (same thing happens for gt0_txcharisk_in[1:0]). I'm using Vivado and the compiler doesn't give me any specific warning. I've also looked at gtwizard example design and I'm not doing anything too different from that.

I'm developing my project on Kintex-7 FPGA.

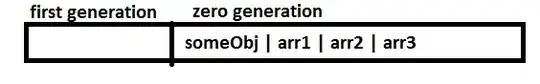

Here is scope and wave window:

Here is my protocol VHDL entity:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity protocol_frame_gen is

Port ( pfg_clk_in : in STD_LOGIC;

pfg_reset_in : in STD_LOGIC;

pfg_data_in : in STD_LOGIC_VECTOR (15 downto 0);

pfg_fifo_empty_in : in STD_LOGIC;

pfg_trasm_rqst_in : in STD_LOGIC;

pfg_fifo_rd_enable_out : out STD_LOGIC;

pfg_data_out : out STD_LOGIC_VECTOR (15 downto 0);

pfg_txcharisk: out STD_LOGIC_VECTOR (1 downto 0)

);

end protocol_frame_gen;

architecture Behavioral of protocol_frame_gen is

type state_type is ( idle, trasmission, dummy_state, end_trasmission);

signal state: state_type;

signal pfg_data_out_reg: STD_LOGIC_VECTOR (15 downto 0):= (others => '0');

signal mux_addr: integer range 0 to 3 := 0;

begin

pfg_data_out <= pfg_data_out_reg;

main: process(pfg_reset_in, pfg_clk_in)

begin

if pfg_reset_in='1' then

state <= idle;

mux_addr <= 0;

pfg_fifo_rd_enable_out <= '0';

elsif rising_edge(pfg_clk_in) then

case state is

when idle =>

if pfg_trasm_rqst_in='1' then

state <= trasmission;

end if;

when trasmission =>

if mux_addr<2 then

mux_addr <= mux_addr+1;

pfg_fifo_rd_enable_out <= '1';

else

null;

end if;

if pfg_fifo_empty_in='1' then

state <= end_trasmission;

pfg_fifo_rd_enable_out <= '0';

mux_addr <= 3;

end if;

when end_trasmission =>

mux_addr <= 0;

state <= idle;

when dummy_state =>

null;

end case;

end if;

end process main;

mux: process (pfg_clk_in)

begin

if rising_edge(pfg_clk_in) then

if mux_addr=0 then

pfg_data_out_reg <= "1111110111111101"; --idle character K29.7 1111110111111101

pfg_txcharisk <= "00";

elsif mux_addr=1 then

pfg_data_out_reg <= "0000000110111100"; --start of frame K28.5 1011110010111100

pfg_txcharisk <= "01";

elsif mux_addr=2 then

pfg_data_out_reg <= pfg_data_in; --valid data

pfg_txcharisk <= "00";

elsif mux_addr=3 then

pfg_data_out_reg <= "0001110000011100"; --end of frame K28.0

pfg_txcharisk <= "00";

end if;

end if;

end process mux;

end Behavioral;

here is wrapper code:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.numeric_std.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_misc.all;

library UNISIM;

use UNISIM.VCOMPONENTS.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

library UNISIM;

use UNISIM.VComponents.all;

entity gtx_interface_wrapper is

Port (--reset

gt_soft_reset_in: in STD_LOGIC;

protocol_reset_in: in STD_LOGIC;

--clocking

GTREFCLK_PAD_P_IN: in STD_LOGIC;

GTREFCLK_PAD_N_IN: in STD_LOGIC;

tx_fifo_clk_out : out STD_LOGIC;

rx_fifo_clk_out : out STD_LOGIC;

fsm_clk_in: in STD_LOGIC;

--tx

tx_data_in : in STD_LOGIC_VECTOR (15 downto 0);

tx_fifo_empty_in : in STD_LOGIC;

tx_trasm_rqst_in : in STD_LOGIC;

tx_fifo_rd_enable_out : out STD_LOGIC;

--rx

rx_data_out : out STD_LOGIC_VECTOR (15 downto 0);

rx_fifo_wren_out : out STD_LOGIC;

--serial I/O

gtxtxp_out: out STD_LOGIC;

gtxtxn_out: out STD_LOGIC;

gtxrxp_in: in STD_LOGIC;

gtxrxn_in: IN STD_LOGIC

);

end gtx_interface_wrapper;

architecture Mapping of gtx_interface_wrapper is

----Component Declaration------

component gtwizard_0

port

(

SOFT_RESET_TX_IN : in std_logic;

SOFT_RESET_RX_IN : in std_logic;

DONT_RESET_ON_DATA_ERROR_IN : in std_logic;

Q0_CLK1_GTREFCLK_PAD_N_IN : in std_logic;

Q0_CLK1_GTREFCLK_PAD_P_IN : in std_logic;

GT0_TX_FSM_RESET_DONE_OUT : out std_logic;

GT0_RX_FSM_RESET_DONE_OUT : out std_logic;

GT0_DATA_VALID_IN : in std_logic;

GT0_TX_MMCM_LOCK_OUT : out std_logic;

GT0_RX_MMCM_LOCK_OUT : out std_logic;

GT0_TXUSRCLK_OUT : out std_logic;

GT0_TXUSRCLK2_OUT : out std_logic;

GT0_RXUSRCLK_OUT : out std_logic;

GT0_RXUSRCLK2_OUT : out std_logic;

gt0_cpllfbclklost_out : out std_logic;

gt0_cplllock_out : out std_logic;

gt0_cpllreset_in : in std_logic;

gt0_drpaddr_in : in std_logic_vector(8 downto 0);

gt0_drpdi_in : in std_logic_vector(15 downto 0);

gt0_drpdo_out : out std_logic_vector(15 downto 0);

gt0_drpen_in : in std_logic;

gt0_drprdy_out : out std_logic;

gt0_drpwe_in : in std_logic;

gt0_dmonitorout_out : out std_logic_vector(7 downto 0);

gt0_eyescanreset_in : in std_logic;

gt0_rxuserrdy_in : in std_logic;

gt0_eyescandataerror_out : out std_logic;

gt0_eyescantrigger_in : in std_logic;

gt0_rxdata_out : out std_logic_vector(15 downto 0);

gt0_rxdisperr_out : out std_logic_vector(1 downto 0);

gt0_rxnotintable_out : out std_logic_vector(1 downto 0);

gt0_gtxrxp_in : in std_logic;

gt0_gtxrxn_in : in std_logic;

gt0_rxdfelpmreset_in : in std_logic;

gt0_rxmonitorout_out : out std_logic_vector(6 downto 0);

gt0_rxmonitorsel_in : in std_logic_vector(1 downto 0);

gt0_rxoutclkfabric_out : out std_logic;

gt0_gtrxreset_in : in std_logic;

gt0_rxpmareset_in : in std_logic;

gt0_rxmcommaalignen_in : in std_logic;

gt0_rxpcommaalignen_in : in std_logic;

gt0_rxchariscomma_out : out std_logic_vector(1 downto 0);

gt0_rxcharisk_out : out std_logic_vector(1 downto 0);

gt0_rxresetdone_out : out std_logic;

gt0_gttxreset_in : in std_logic;

gt0_txuserrdy_in : in std_logic;

gt0_txdata_in : in std_logic_vector(15 downto 0);

gt0_gtxtxn_out : out std_logic;

gt0_gtxtxp_out : out std_logic;

gt0_txoutclkfabric_out : out std_logic;

gt0_txoutclkpcs_out : out std_logic;

gt0_txcharisk_in : in std_logic_vector(1 downto 0);

gt0_txresetdone_out : out std_logic;

GT0_QPLLOUTCLK_OUT : out std_logic;

GT0_QPLLOUTREFCLK_OUT : out std_logic;

sysclk_in : in std_logic

);

end component;

component protocol_frame_gen

port

(

pfg_clk_in : in STD_LOGIC;

pfg_reset_in : in STD_LOGIC;

pfg_data_in : in STD_LOGIC_VECTOR (15 downto 0);

pfg_fifo_empty_in : in STD_LOGIC;

pfg_trasm_rqst_in : in STD_LOGIC;

pfg_fifo_rd_enable_out : out STD_LOGIC;

pfg_data_out : out STD_LOGIC_VECTOR (15 downto 0);

pfg_txcharisk: out STD_LOGIC_VECTOR (1 downto 0)

);

end component;

component protocol_frame_check

port

(

pfc_clk_in : in STD_LOGIC;

pfc_reset_in : in STD_LOGIC;

pfc_data_in : in STD_LOGIC_VECTOR (15 downto 0);

pfc_data_out : out STD_LOGIC_VECTOR (15 downto 0);

pfc_fifo_wren_out : out STD_LOGIC

);

end component;

--_______________________INTERNAL REGISTER______________________--

--gt0 I/O registers

signal SOFT_RESET_TX_IN_i: std_logic;

signal SOFT_RESET_RX_IN_i: std_logic;

signal DONT_RESET_ON_DATA_ERROR_IN_i: std_logic;

signal Q0_CLK1_GTREFCLK_PAD_N_IN_i: std_logic;

signal Q0_CLK1_GTREFCLK_PAD_P_IN_i: std_logic;

signal GT0_TX_FSM_RESET_DONE_OUT_i: std_logic;

signal GT0_RX_FSM_RESET_DONE_OUT_i: std_logic;

signal GT0_DATA_VALID_IN_i: std_logic;

signal GT0_TX_MMCM_LOCK_OUT_i: std_logic;

signal GT0_RX_MMCM_LOCK_OUT_i: std_logic;

signal GT0_TXUSRCLK_OUT_i: std_logic;

signal GT0_TXUSRCLK2_OUT_i: std_logic;

signal GT0_RXUSRCLK_OUT_i: std_logic;

signal GT0_RXUSRCLK2_OUT_i: std_logic;

signal gt0_cpllfbclklost_out_i: std_logic;

signal gt0_cplllock_out_i: std_logic;

signal gt0_cpllreset_in_i: std_logic;

signal gt0_drpaddr_in_i: std_logic_vector(8 downto 0);

signal gt0_drpdi_in_i: std_logic_vector(15 downto 0);

signal gt0_drpdo_out_i: std_logic_vector(15 downto 0);

signal gt0_drpen_in_i: std_logic;

signal gt0_drprdy_out_i: std_logic;

signal gt0_drpwe_in_i: std_logic;

signal gt0_dmonitorout_out_i: std_logic_vector(7 downto 0);

signal gt0_eyescanreset_in_i: std_logic;

signal gt0_rxuserrdy_in_i: std_logic;

signal gt0_eyescandataerror_out_i: std_logic;

signal gt0_eyescantrigger_in_i: std_logic;

signal gt0_rxdata_out_i: std_logic_vector(15 downto 0);

signal gt0_rxdisperr_out_i: std_logic_vector(1 downto 0);

signal gt0_rxnotintable_out_i: std_logic_vector(1 downto 0);

signal gt0_gtxrxp_in_i: std_logic;

signal gt0_gtxrxn_in_i: std_logic;

signal gt0_rxdfelpmreset_in_i: std_logic;

signal gt0_rxmonitorout_out_i: std_logic_vector(6 downto 0);

signal gt0_rxmonitorsel_in_i: std_logic_vector(1 downto 0);

signal gt0_rxoutclkfabric_out_i: std_logic;

signal gt0_gtrxreset_in_i: std_logic;

signal gt0_rxpmareset_in_i: std_logic;

signal gt0_rxmcommaalignen_in_i: std_logic;

signal gt0_rxpcommaalignen_in_i: std_logic;

signal gt0_rxchariscomma_out_i: std_logic_vector(1 downto 0);

signal gt0_rxcharisk_out_i: std_logic_vector(1 downto 0);

signal gt0_rxresetdone_out_i: std_logic;

signal gt0_gttxreset_in_i: std_logic;

signal gt0_txuserrdy_in_i: std_logic;

signal gt0_txdata_in_i: std_logic_vector(15 downto 0);

signal gt0_gtxtxn_out_i: std_logic;

signal gt0_gtxtxp_out_i: std_logic;

signal gt0_txoutclkfabric_out_i: std_logic;

signal gt0_txoutclkpcs_out_i: std_logic;

signal gt0_txcharisk_in_i: std_logic_vector(1 downto 0);

signal gt0_txresetdone_out_i: std_logic;

signal GT0_QPLLOUTCLK_OUT_i: std_logic;

signal GT0_QPLLOUTREFCLK_OUT_i: std_logic;

signal sysclk_in_i: std_logic ;

--frame generator

signal pfg_clk_in_i: STD_LOGIC;

signal pfg_reset_in_i: STD_LOGIC;

signal pfg_data_in_i: STD_LOGIC_VECTOR (15 downto 0);

signal pfg_fifo_empty_in_i: STD_LOGIC;

signal pfg_trasm_rqst_in_i: STD_LOGIC;

signal pfg_fifo_rd_enable_out_i: STD_LOGIC;

signal pfg_data_out_i: STD_LOGIC_VECTOR (15 downto 0) ;

signal pfg_txcharisk_i: std_logic_vector(1 downto 0);

--frame checker

signal pfc_clk_in_i: STD_LOGIC;

signal pfc_reset_in_i: STD_LOGIC;

signal pfc_data_in_i: STD_LOGIC_VECTOR (15 downto 0);

signal pfc_data_out_i: STD_LOGIC_VECTOR (15 downto 0);

signal pfc_fifo_wren_out_i: STD_LOGIC;

begin

unit_gt0: gtwizard_0 port map ( SOFT_RESET_TX_IN => SOFT_RESET_TX_IN_i,

SOFT_RESET_RX_IN => SOFT_RESET_RX_IN_i,

DONT_RESET_ON_DATA_ERROR_IN => DONT_RESET_ON_DATA_ERROR_IN_i,

Q0_CLK1_GTREFCLK_PAD_N_IN => Q0_CLK1_GTREFCLK_PAD_N_IN_i,

Q0_CLK1_GTREFCLK_PAD_P_IN => Q0_CLK1_GTREFCLK_PAD_P_IN_i,

GT0_TX_FSM_RESET_DONE_OUT => GT0_TX_FSM_RESET_DONE_OUT_i,

GT0_RX_FSM_RESET_DONE_OUT => GT0_RX_FSM_RESET_DONE_OUT_i,

GT0_DATA_VALID_IN => GT0_DATA_VALID_IN_i,

GT0_TX_MMCM_LOCK_OUT => GT0_TX_MMCM_LOCK_OUT_i,

GT0_RX_MMCM_LOCK_OUT => GT0_RX_MMCM_LOCK_OUT_i,

GT0_TXUSRCLK_OUT => GT0_TXUSRCLK_OUT_i,

GT0_TXUSRCLK2_OUT => GT0_TXUSRCLK2_OUT_i,

GT0_RXUSRCLK_OUT => GT0_RXUSRCLK_OUT_i,

GT0_RXUSRCLK2_OUT => GT0_RXUSRCLK2_OUT_i,

gt0_cpllfbclklost_out => gt0_cpllfbclklost_out_i,

gt0_cplllock_out => gt0_cplllock_out_i,

gt0_cpllreset_in => gt0_cpllreset_in_i,

gt0_drpaddr_in => gt0_drpaddr_in_i,

gt0_drpdi_in => gt0_drpdi_in_i,

gt0_drpdo_out => gt0_drpdo_out_i,

gt0_drpen_in => gt0_drpen_in_i,

gt0_drprdy_out => gt0_drprdy_out_i,

gt0_drpwe_in => gt0_drpwe_in_i,

gt0_dmonitorout_out => gt0_dmonitorout_out_i,

gt0_eyescanreset_in => gt0_eyescanreset_in_i,

gt0_rxuserrdy_in => gt0_rxuserrdy_in_i,

gt0_eyescandataerror_out => gt0_eyescandataerror_out_i,

gt0_eyescantrigger_in => gt0_eyescantrigger_in_i,

gt0_rxdata_out => gt0_rxdata_out_i,

gt0_rxdisperr_out => gt0_rxdisperr_out_i,

gt0_rxnotintable_out => gt0_rxnotintable_out_i,

gt0_gtxrxp_in => gt0_gtxrxp_in_i,

gt0_gtxrxn_in => gt0_gtxrxn_in_i,

gt0_rxdfelpmreset_in => gt0_rxdfelpmreset_in_i,

gt0_rxmonitorout_out => gt0_rxmonitorout_out_i,

gt0_rxmonitorsel_in => gt0_rxmonitorsel_in_i,

gt0_rxoutclkfabric_out => gt0_rxoutclkfabric_out_i,

gt0_gtrxreset_in => gt0_gtrxreset_in_i,

gt0_rxpmareset_in => gt0_rxpmareset_in_i,

gt0_rxmcommaalignen_in => gt0_rxmcommaalignen_in_i,

gt0_rxpcommaalignen_in => gt0_rxpcommaalignen_in_i,

gt0_rxchariscomma_out => gt0_rxchariscomma_out_i,

gt0_rxcharisk_out => gt0_rxcharisk_out_i,

gt0_rxresetdone_out => gt0_rxresetdone_out_i,

gt0_gttxreset_in => gt0_gttxreset_in_i,

gt0_txuserrdy_in => gt0_txuserrdy_in_i,

gt0_txdata_in => gt0_txdata_in_i,

gt0_gtxtxn_out => gt0_gtxtxn_out_i,

gt0_gtxtxp_out => gt0_gtxtxp_out_i,

gt0_txoutclkfabric_out => gt0_txoutclkfabric_out_i,

gt0_txoutclkpcs_out => gt0_txoutclkpcs_out_i,

gt0_txcharisk_in => gt0_txcharisk_in_i,

gt0_txresetdone_out => gt0_txresetdone_out_i,

GT0_QPLLOUTCLK_OUT => GT0_QPLLOUTCLK_OUT_i,

GT0_QPLLOUTREFCLK_OUT => GT0_QPLLOUTREFCLK_OUT_i,

sysclk_in => sysclk_in_i );

unit_pfg: protocol_frame_gen port map ( pfg_clk_in => pfg_clk_in_i,

pfg_reset_in => pfg_reset_in_i,

pfg_data_in => pfg_data_in_i,

pfg_fifo_empty_in => pfg_fifo_empty_in_i,

pfg_trasm_rqst_in => pfg_trasm_rqst_in_i,

pfg_fifo_rd_enable_out => pfg_fifo_rd_enable_out_i,

pfg_data_out => pfg_data_out_i,

pfg_txcharisk => pfg_txcharisk_i );

unit_pfc: protocol_frame_check port map ( pfc_clk_in => pfc_clk_in_i,

pfc_reset_in => pfc_reset_in_i,

pfc_data_in => pfc_data_in_i,

pfc_data_out => pfc_data_out_i,

pfc_fifo_wren_out => pfc_fifo_wren_out_i );

--_______________EXTERNAL WIRING_______________--

--reset

SOFT_RESET_TX_IN_i <= gt_soft_reset_in;

SOFT_RESET_RX_IN_i <= gt_soft_reset_in;

pfg_reset_in_i <= protocol_reset_in;

pfc_reset_in_i <= protocol_reset_in;

--clocking (refclk has IBUF declaration)

Q0_CLK1_GTREFCLK_PAD_P_IN_i <= GTREFCLK_PAD_P_IN;

Q0_CLK1_GTREFCLK_PAD_N_IN_i <= GTREFCLK_PAD_N_IN;

tx_fifo_clk_out <= GT0_TXUSRCLK2_OUT_i;

rx_fifo_clk_out <= GT0_RXUSRCLK2_OUT_i;

sysclk_in_i <= fsm_clk_in;

--tx

pfg_data_in_i <= tx_data_in;

pfg_fifo_empty_in_i <= tx_fifo_empty_in;

pfg_trasm_rqst_in_i <= tx_trasm_rqst_in;

tx_fifo_rd_enable_out <= pfg_fifo_rd_enable_out_i;

--rx

rx_data_out <= pfc_data_out_i;

rx_fifo_wren_out <= pfc_fifo_wren_out_i;

--serial I/O

gtxtxp_out <= gt0_gtxtxp_out_i;

gtxtxn_out <= gt0_gtxtxn_out_i;

gt0_gtxrxp_in_i <= gtxrxp_in;

gt0_gtxrxn_in_i <= gtxrxn_in;

--_______________INTERNAL WIRING_______________--

--protocol clocking

pfg_clk_in_i <= GT0_TXUSRCLK2_OUT_i;

pfc_clk_in_i <= GT0_RXUSRCLK2_OUT_i;

--datapath

gt0_txdata_in_i <= pfg_data_out_i;

pfc_data_in_i <= gt0_rxdata_out_i;

--gt0 configuration: these signals are all tied to groung for

--proper gt funciotning

gt0_rxdfelpmreset_in_i <= '0';

gt0_gtrxreset_in_i <= '0';

gt0_rxpmareset_in_i <= '0';

gt0_cpllreset_in_i <= '0';

--DRP ports are not used

gt0_drpaddr_in_i <= (others => '0');

gt0_drpdi_in_i <= (others => '0');

gt0_drpen_in_i <= '0';

gt0_drpwe_in_i <= '0';

gt0_eyescanreset_in_i <= '0';

gt0_eyescantrigger_in_i <= '0';

gt0_gttxreset_in_i <= '0';

gt0_rxmonitorsel_in_i <= (others => '0');

gt0_txuserrdy_in_i <= '1';

gt0_rxuserrdy_in_i <= '1';

--gt0 configuration: these signals are all tied to power for

--proper gt funciotning

gt0_txcharisk_in_i <= pfg_txcharisk_i;

gt0_rxmcommaalignen_in_i <= '1';

gt0_rxpcommaalignen_in_i <= '1';

DONT_RESET_ON_DATA_ERROR_IN_i <= '0';

end Mapping;