I'm working on a project in which I need a bidirectional tri-state buffer. I've developed a VHDL code based on my searches in this community and some other websites. But it doesn't work as it should. Below is the VHDL code.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity Inter_Con_Mod is

generic(WL: integer := 8);

port(In1: in signed(WL-1 downto 0);

RW: in std_logic;

Data_IO1: inout signed(WL-1 downto 0);

Out1: out signed(WL-1 downto 0));

end Inter_Con_Mod;

architecture Behav of Inter_Con_Mod is

begin

Data_IO1 <= In1 when RW = '1' else

(others => 'Z');

Out1 <= Data_IO1;

end Behav;

This is the testbench code:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY InterCon_test IS

END InterCon_test;

ARCHITECTURE behavior OF InterCon_test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT Inter_Con_Mod

PORT(

In1 : IN signed(7 downto 0);

RW : IN std_logic;

Data_IO1 : INOUT signed(7 downto 0);

Out1 : OUT signed(7 downto 0)

);

END COMPONENT;

--Inputs

signal In1 : signed(7 downto 0) := (others => '0');

signal RW : std_logic := '0';

--BiDirs

signal Data_IO1 : signed(7 downto 0);

--Outputs

signal Out1 : signed(7 downto 0);

-- No clocks detected in port list. Replace <clock> below with

-- appropriate port name

--constant <clock>_period : time := 10 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: Inter_Con_Mod PORT MAP (

In1 => In1,

RW => RW,

Data_IO1 => Data_IO1,

Out1 => Out1

);

-- Clock process definitions

-- Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for 5 ns;

In1 <= "01111111";

wait for 5 ns;

RW <= '1';

wait for 5 ns;

RW <= '0';

wait for 20 ns;

Data_IO1 <= "00101010";

wait;

end process;

END;

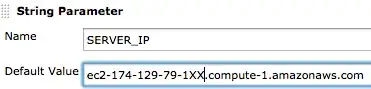

But look what happens in the simulation Result:

I don't get why it ignores the test bench stimulation I've provided before setting RW to 0.

Thanks in advance.