(edited) i'm working on the verilog Arithmetic project and i got stuck on the sign extension part(assuming this is the problem). i have 4bit input A, B and should have 8 bit output. for some of the process(sum, sub...) i need to use sign extend to make the 8bit output. so for the body of arithmetic, i have this code. this is half of the code. i didn't include the half part cuz it's just long..

module arithmetic(A, B, AN0, DP, sum, sub, mult, div, comp, shiftLeft,

shiftRight, signExtend);

input signed [3:0] A, B;

output [7:0] sum, sub, mult, div, comp, shiftLeft, shiftRight,

signExtend;

output AN0, DP;

//sum

reg [4:0] qsum;

always@ (A, B)

qsum = A+B;

assign sum = {{3{qsum[4]}},qsum};

//sub

reg [4:0] qsub;

always@ (A, B)

qsub = A-B;

assign sub = {{3{qsub[4]}},qsub};

//mult

reg [7:0] qmult;

always@ (A, B)

qmult = A * B;

assign mult = qmult;

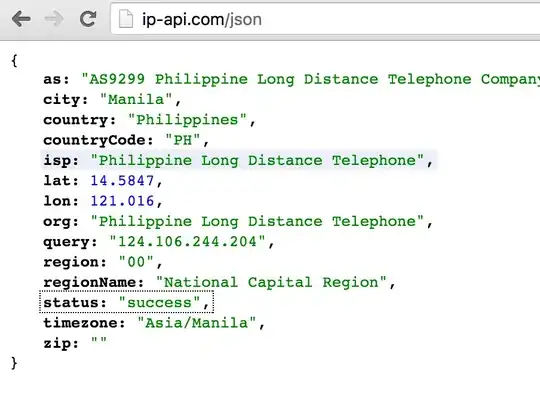

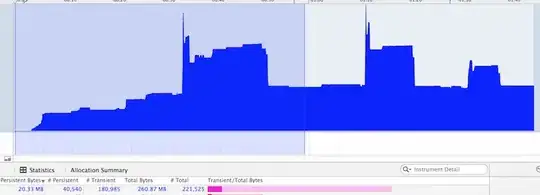

and when i checked my simulation, it doesn't have any values but Z, and Xs. it doesn't even show any input values. why is that happening?? thank you

(edited) this is my test bench code. there are 8 operations(sum, subtract, multiply, division, comparator, shiftleft, shiftright, sign extension)

module lap3_top_tb();

reg signed [3:0] A, B;

reg [2:0] Operation;

wire [7:0] Result;

wire DP, AN0;

lab3_top ulap3_top(

.A(A),

.B(B),

.Operation(Operation),

.Result(Result),

.DP(DP),

.AN0(AN0)

);

initial begin

A = 6; B = 7; Operation = 0;

#20;

A = -6; B = -7; Operation = 0;

#20;

A = 6; B = 7; Operation = 1;

#20;

A = -6; B = -7; Operation = 1;

#20;

A = 6; B = 7; Operation = 2;

#20;

A = -6; B = 7; Operation = 2;

#20;

A = 7; B = 4; Operation = 3;

#20;

A = 7; B = 0; Operation = 3;

#20;

A = 6; B = 7; Operation = 4;

#20;

A = -6; B = -7; Operation = 4;

#20;

A = 1; B = 6; Operation = 5;

#20;

A = 1; B = -6; Operation = 5;

#20;

A = 1; B = 6; Operation = 6;

#20;

A = 1; B = -6; Operation = 6;

#20;

A = 6; B = 0; Operation = 7;

#20;

A = -5; B = 0; Operation = 7;

#20;

end

endmodule

the lap3_top file is here. (mux_8_1 will pick the output and out thru Result. if you need code, let me know! but i think mux works fine)

module lap3_top(A, B, Operation, Result, AN0, DP);

input signed [3:0] A, B;

input [2:0] Operation;

output AN0, DP;

output [7:0] Result;

wire a, b, c, d, e, f, g, h;

arithmetic uarithmetic(

.A(A),

.B(B),

.AN0(AN0),

.DP(DP),

.sum(a),

.sub(b),

.mult(c),

.div(d),

.comp(e),

.shiftLeft(f),

.shiftRight(g),

.signExtend(h)

);

mux_8_1 umux8_1(

.A(a),

.B(b),

.C(c),

.D(d),

.E(e),

.F(f),

.G(g),

.H(h),

.Operation(Operation),

.Result(Result)

);

endmodule

thank you so much guys!