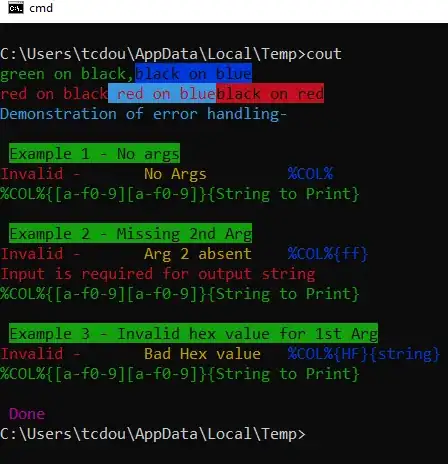

im making an ALU with an option to do A + 2B but im having trouble getting my head around multiplying the 2B and getting the proper answer in my test bench.

EG: A = 0110 B = 0011 Equation is A + 2B and im getting 0110

a snippit of my code is

entity ALU is

port( A :IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;

B :IN STD_LOGIC_VECTOR(3 DOWNTO 0) ;

S0 :IN STD_LOGIC ;

S1 :IN STD_LOGIC ;

M :IN STD_LOGIC ;

C0 :IN STD_LOGIC ;

Cout :OUT STD_LOGIC ;

Z :OUT STD_LOGIC ;

F :OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

SIGNAL VariableAlu : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL FTEMP : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL FTEMP2 : STD_LOGIC_VECTOR(4 DOWNTO 0);

SIGNAL ZTEMP : STD_LOGIC;

SIGNAL BTEMP1 : STD_LOGIC_VECTOR(4 DOWNTO 0);

END ALU ;

PROCESS(A,B,S0,S1,M,C0)

BEGIN

VariableAlu <= (S0 & S1 & C0 & M);

--M = 1 ARITHMETIC

(part that shifts it, lab teacher told us to do this)

BTEMP1(4 DOWNTO 1)<= B;

BTEMP1(0)<= '0';

when "1111" => FTEMP2 <= ((A) + BTEMP1);

any help would be greatly appreciated.