I wrote a simple full adder which uses 2 half adders and an OR gate. The VHDL code is pretty simple

library ieee;

use ieee.std_logic_1164.all;

entity ha is

port( x: in std_logic;

y: in std_logic;

s: out std_logic;

c: out std_logic);

end;

architecture x of ha is

begin

s <= x xor y;

c <= x and y;

end;

and

library ieee;

use ieee.std_logic_1164.all;

entity fa is

port( a: in std_logic; b: in std_logic; cin: in std_logic;

sum: out std_logic; cout: out std_logic);

end;

architecture y of fa is

component ha port( x: in std_logic; y: in std_logic;

s: out std_logic; c: out std_logic);

end component;

signal im1, im2, im3: std_logic;

begin

ha1: ha port map( x=>a, y=>b, s=>im1, c=>im2 );

ha2: ha port map( x=>im1, y=>cin, s=>sum, c=>im3 );

cout <= im3 or im2;

end;

The output of the synthesizer however shows there are two XOR gates. Where are the OR gate and others for half adder?

=========================================================================

* Advanced HDL Synthesis *

=========================================================================

Advanced HDL Synthesis Report

Macro Statistics

# Xors : 2

1-bit xor2 : 2

=========================================================================

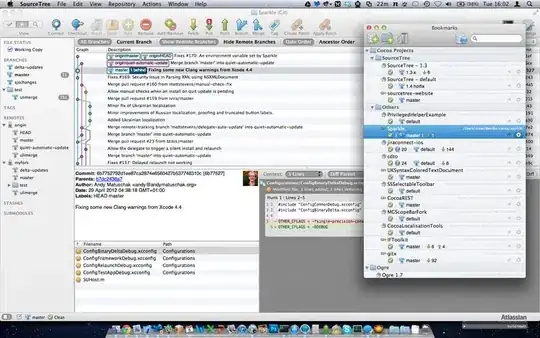

Also, the RTL schematic of the FA is correct, however, the RTL schematic of the half adder is weird! The y port is not present and there is data[1:0]. What does that mean?

FA:

HA: