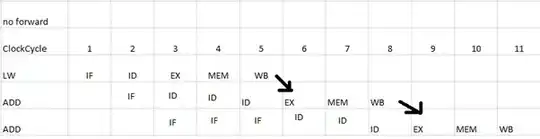

Assembly Code:

lw R1, 0(R2)

add R4, R3, R1

add R3, R1, R4

What are the dependencies?

Fill the pipelining timeline if:

a. There is forwarding

b. There is no forwarding

Instruction 1 and 2 have a dependency for R1. Instruction 2 and 3 have a dependency for R4.

Below are my two attempts for part a and part b respectively:

Am I filling the pipelining timeline correctly?