I am a Verilog user trying to make sense of VHDL code of AXI4 Master bus functional model (BFM)

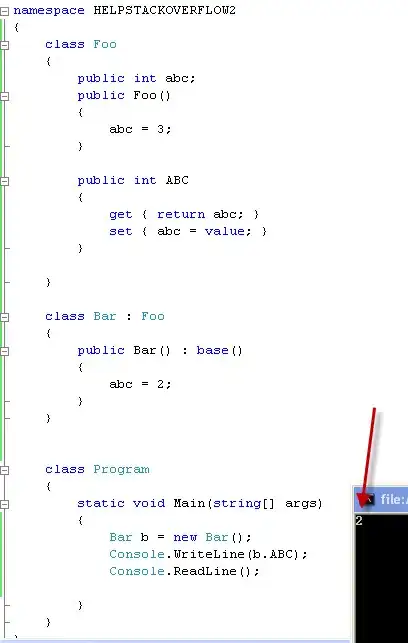

AXI4 Master Bus functional model VHDL code

I have a few questions from the above code

What would block diagram of the code look like (how are components connected with each other)

Lastly, what is the use of FIFO? I mean to connect AXI master to AXI slave, can't one connect the appropriate signals directly as shown in the picture? What purpose does FIFO serve here and what if it is removed?