Although I have completed a university course in digital logic, I am new to VHDL design and I am hoping if someone can help me create 2 clock signals which depend on the state of one another.

I am using a 50 MHz clock on a DE2-115 FPGA board that is used to create a 5MHz clock (named dclk_5). However, the simulation is showing the two signal but only up to 200 ns of run time and won't run any longer. Why doesnt the simulation run longer than 200 ns?

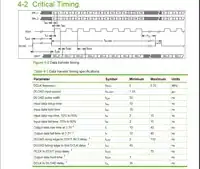

datasheet of the 2 clocks:

Alternative VHDL Design for testing dclk_5 and clk_50 which synthesizes but simulation is not correct:

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity DCLK_top is

port(

clk_50 : in std_logic;

sw : in std_logic;

dclk_5 : out std_logic

);

end DCLK_top;

architecture behaviour of DCLK_top is

signal clk_counter : integer range 0 to 10 := 0;

signal dclk_counter : integer range 0 to 8 := 0;

signal dclk_pause_counter : integer range 0 to 7 := 0;

signal dclk_pause : std_logic := '0';

signal clk_pause_counter : integer range 0 to 7 := 0;

begin

dclk_proc : process(clk_50)

begin

if(clk_50'event and clk_50='1' ) then

clk_counter <= clk_counter+1;

if(clk_counter=10) then

clk_counter <= 0;

end if;

if(clk_counter<5) then

dclk_5 <= '0';

else

dclk_5 <= '1';

end if;

end if;

end process dclk_proc;

end architecture behaviour;

Picture of simulation: