I have the following simple FSM description in VHDL:

library ieee;

use ieee.std_logic_1164.all;

entity coverage1 is

port (

clk : in std_logic;

rst : in std_logic;

req : in std_logic;

ack : out std_logic

);

end entity coverage1;

architecture rtl of coverage1 is

type STATES is (IDLE, RUNNING, FINISH);

signal fsm_cs : STATES := IDLE;

signal fsm_ns : STATES;

begin

process (fsm_cs, req) is

begin

fsm_ns <= fsm_cs;

ack <= '0';

case fsm_cs is

when IDLE =>

if req = '1' then

fsm_ns <= RUNNING;

end if;

when RUNNING =>

fsm_ns <= FINISH;

when FINISH =>

ack <= '1';

fsm_ns <= IDLE;

when others =>

null;

end case;

end process;

process (clk) is

begin

if rising_edge(clk) then

if rst = '1' then

fsm_cs <= IDLE;

else

fsm_cs <= fsm_ns;

end if;

end if;

end process;

end architecture;

And this testbench:

library ieee;

use ieee.std_logic_1164.all;

entity coverage1_tb is

end entity coverage1_tb;

architecture tb of coverage1_tb is

signal clk : std_logic := '1';

signal rst : std_logic;

signal req : std_logic;

signal ack : std_logic;

signal finished : boolean := false;

begin

coverage1_1: entity work.coverage1

port map (

clk => clk,

rst => rst,

req => req,

rdy => rdy,

ack => ack);

clk <= not clk after 5 ns when not finished else unaffected;

process

begin

rst <= '1';

wait until rising_edge(clk);

rst <= '0';

req <= '0';

wait until rising_edge(clk);

req <= '1';

wait until rising_edge(clk);

req <= '0';

wait until rising_edge(clk) and ack = '1';

wait until rising_edge(clk);

finished <= true;

wait;

end process;

end architecture tb;

The FSM does not reach 100% code coverage in ModelSim/QuestaSim. I found two issues:

The others case, which is not required because the enumeration is fully covered by all choices, is requested to be covered. But this branch is not reachable... Why does QuestaSim expect coverage for this branch?

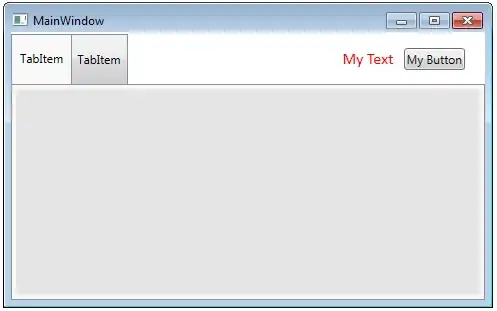

QuestaSim shows a false state diagram for my example FSM. The diagram contains self-edges for the states:

RUNNINGandFINISH. These edges do not exist nor can they be covered.

If I remove the default assignmentfsm_ns <= fsm_cs;and add an else branch in the IDLE state, I'll get full coverage.if req = '1' then fsm_ns <= RUNNING; else fsm_ns <= IDLE; end if;Why does the state diagram show false edges and why can't I use default assignments?

I could live with bullet item 1, but item 2 is a problem. If I write my FSMs in that style, I'm duplicating a lot of unneeded code and most synthesizers won't recognize the FSM pattern! So I'll lose FSM optimizations and checking in synthesis.