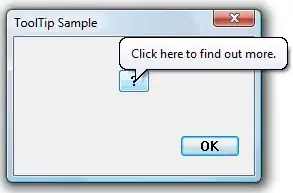

Neon (advanced SIMD) is very fast for add,subtract,multiply and floating point operations like single precision and double precision. Why ARM company still have another separate unit for floating point calculation as you can see in picture. i am little bit confused about it.

Asked

Active

Viewed 666 times

-2

-

4Because pretty marketing pictures aren't accurate documentation of microarchitecture? – Notlikethat May 27 '16 at 10:43

-

This one is not right answer. not satisfactory . – Jawwad Rafiq May 27 '16 at 10:54

-

3It's not an answer - it's a comment pointing out that the question is invalid because it's based on incorrect assumptions: NEON does not do double-precision - a NEON-capable FPU still implements VFP instructions for that - and [Cortex-A9's data engine options are _mutually exclusive_](http://infocenter.arm.com/help/topic/com.arm.doc.ddi0388g/BABCICDB.html). The arbitrary boxes on the marketing picture do not in any way represent the actual pipeline. – Notlikethat May 27 '16 at 11:39

-

2The FPU pre-dates NEON. NEON is SIMD an FPU is not multiple data, only a single float at a time. Both consume silicon and are optional elements in many Cortex CPUs. However, when present both behave the same across the family. – artless noise May 27 '16 at 12:51

-

The Cortex-A9 NEON MPE hardware supports single and double precision add, subtract, multiply, divide, multiply and accumulate, and square root operations. [infocenter.arm.com/help/topic/.../DDI0409G_cortex_a9_neon_mpe_r3p0_trm.pdf] . how can you say that, its not double precision. if you have not knowledge about anything, you should have not said it invalid question . – Jawwad Rafiq May 27 '16 at 15:36

-

Yes, because the Cortex-A9 "NEON Media Processing Engine" option implements both the NEON instruction set - which operates on vectors of integers or single-precision floating-point values - _and_ the VFP instruction set, which operates on scalar single-precision and double-precision values. The reduced "Floating-point unit" option _only_ implements VFP instructions (and only has half as many registers). To pre-empt any further wild accusations, yes it's true that AArch64 NEON in ARMv8 does add double-precision vector operations, but that's entirely irrelevant to Cortex-A9. – Notlikethat May 27 '16 at 18:45

-

3I'm voting to close this question as off-topic because it does not deal with a specific programming-related issue. – Jules May 28 '16 at 01:54

1 Answers

2

This is mostly as an illustration, and also because Floating-Point and Neon are two separate instruction sets before ARMv8-A or in Aarch32. And Neon only supports a subset of floating-point support (No double precision).

This was clearly the case for Cortex-A9, shown on the illustration.

However this is not true anymore in ARMv8-A Aarch64 in which there is no such split. There is instead a SIMD versus Scalar split, and SIMD instructions can use 64-bit floating-point numbers.

Dric512

- 3,525

- 1

- 20

- 27

-

1There are some technical differences too - e.g. handling of IEE corner cases, such as Inf, NaN, and denomals. The NEON requirements are rather more relaxed than than the full VFP IEE scalar floats, so NEON isn't a drop-in replacement, even for fp32. – solidpixel Jun 03 '16 at 12:51

-

1