I am very new on verilog. So this is my question:

Implement 16 bits ALU with 16 bit register. This project should meet the following requirement.

1. Design a 16 bitALU : Design a 16 bit ALU that X as input (eg. A,B..) and produces one 16 bit result.The ALU should perform the following functions. Minimum 5 operations for both ALU and LOGIC.

2. Design a 16x16 bit register file.

3. Design a control unit.

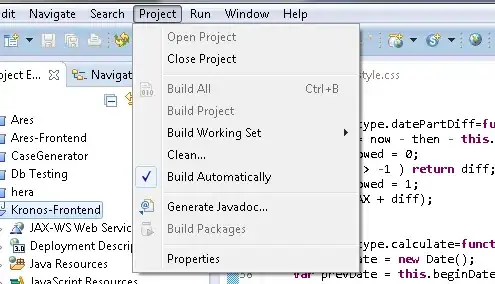

So my plan is to make a bunch of module that have operations in each module. Then i gather it at the test bench. But the problem is right now. The output seems to overlap and become red and x.

This is my Add module.

module Add(A,B,Y,S,clk,enb);

parameter BITS=8;

input clk,enb;

input [BITS - 5:0] S;

input [BITS - 1:0] A ,B;

output [BITS - 1:0] Y;

reg [BITS - 1:0] Y;

always @(posedge clk)

begin

if

((enb==1) || (S == 000))

begin

assign Y = A + B;

end

end

endmodule

Tolak module (Minus module)

module Tolak(A,B,Y,S,clk,enb);

parameter BITS=8;

input clk,enb;

input [BITS - 5:0] S;

input [BITS - 1:0] A ,B;

output [BITS - 1:0] Y;

reg [BITS - 1:0] Y;

always @(posedge clk)

begin

if

((enb==1) || (S == 010))

begin

assign Y = A - B;

end

end

endmodule

Darab module (Multiplication module)

module Darab(A,B,Y,S,clk,enb);

parameter BITS=8;

input clk,enb;

input [BITS - 5:0] S;

input [BITS - 1:0] A ,B;

output [BITS - 1:0] Y;

reg [BITS - 1:0] Y;

always @(posedge clk)

begin

if

((enb==1) || (S == 011))

begin

assign Y = A * B;

end

end

endmodule

GateOr module

module GateOr(A,B,Y,S,clk,enb);

parameter BITS=16;

input clk,enb;

input [BITS - 14:0] S;

input [BITS - 1:0] A ,B;

output [BITS - 1:0] Y;

reg [BITS - 1:0] Y;

always @(posedge clk)

begin

if

((enb==1) || (S == 011))

begin

assign Y = A | B ;

end

end

endmodule

GateAnd module

module GateAnd(A,B,Y,S,clk,enb);

parameter BITS=16;

input clk,enb;

input [BITS - 14:0] S;

input [BITS - 1:0] A ,B;

output [BITS - 1:0] Y;

reg [BITS - 1:0] Y;

always @(posedge clk)

begin

if

((enb==1) || (S == 100))

begin

assign Y = A & B;

end

end

endmodule

AND THIS IS MY TEST BENCH

module Maintb ();

parameter SIZE=8;

reg clk, enb ;

reg [SIZE-6:0] S;

reg[SIZE-1:0] A,B;

wire[SIZE-1:0] Y;

initial

begin

clk = 1'b0; enb = 1'b0;

end

// generate clock

always

begin

#(10) clk = !clk;

end

always begin

//#(10);

#10; enb = 1'b1; A=00000001; B=00000000; S=000; //add

#(10); enb = 1'b0;

#10; enb = 1'b1; A=00000001; B=00000000; S=001; //tolak

#(10); enb = 1'b0;

#10; enb = 1'b1; A=00000001; B=00000000; S=010; //darab

#(10); enb = 1'b0;

#10; enb = 1'b1; A=00000001; B=00000000; S=011; //or

#(10); enb = 1'b0;

#10; enb = 1'b1; A=00000001; B=00000000; S=100; //and

//#(10);

end

defparam dut.BITS = SIZE;

defparam dut1.BITS = SIZE;

defparam dut2.BITS = SIZE;

defparam gate.BITS = SIZE;

defparam gate1.BITS = SIZE;

Add dut (A,B,Y,S,clk,enb); //000

Tolak dut1 (A,B,Y,S,clk,enb); //001

Darab dut2 (A,B,Y,S,clk,enb); //010

GateOr gate (A,B,Y,S,clk,enb); //011

GateAnd gate1 (A,B,Y,S,clk,enb);//100

Endmodule