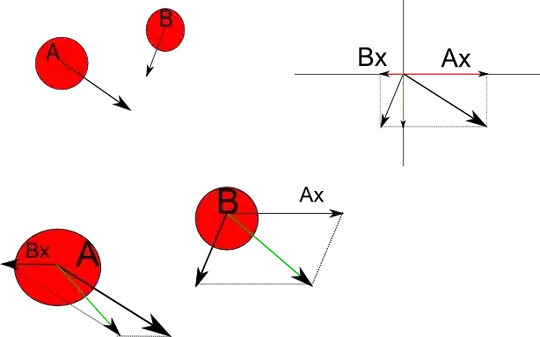

What I want to do is add the element 0+11, then 1+10, then 2+9 and like this with all the others, but when I'm simulating, it takes just the first elements (0,11). I also thought it will be a good idea to take the values in one clock event but I'm not sure.

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use ieee.std_logic_unsigned.all;

entity Sumador is

Port ( clk : in STD_LOGIC;

en : in STD_LOGIC;

--actCont : in STD_LOGIC;

data : out STD_LOGIC_VECTOR (6 downto 0);

A,B: inout STD_LOGIC_VECTOR (6 downto 0);

C: inout STD_LOGIC_VECTOR (6 downto 0)

);

end Sumador;

architecture Behavioral of Sumador is

signal addr: STD_LOGIC_VECTOR(3 downto 0);

--signal A,B,C: STD_LOGIC_VECTOR(6 downto 0);

type arrayRom is array (0 to 11) of std_logic_vector(6 downto 0);

constant memRom: arrayRom:=(

"1111111",--0

"1001111",--1

"0010010",--2

"0000110",--3

"1001100",--4

"0100000",--5

"0001111",--6

"0000000",--7

"0001100",--8

"0000001",--9

"0001000",--10

"0100001"

);

begin

process(clk)

begin

if(RISING_EDGE(clk))then

if(en='1')then

for i in 0 to 11 loop

A<=memRom(i); --here i get the value from the i position of the constant memory

B<=memRom(11-i);

C<=A+B;

end loop;

data<=C;

else

--A<="0000000";

--B<="0000000";

--C<=A+B;

--data<=C;

data<="0000000";

end if;

end if;

end process;

end Behavioral;`enter code here`

on test bench

enter code here

-- Stimulus process

stim_proc: process

begin

en<='0';

wait for 100 ns;

en<='1';

wait for 100 ns;

en<='0';

wait for 100 ns;

en<='1';

wait for 100 ns;

en<='0';

wait for 100 ns;

en<='1';

wait;

end process;

Some simulation results: