I am using Xilinx IDE. My ALU module is as follows:

module ALU(in1,in2,operation,clk,out

);

input [15:0] in1;

input [15:0] in2;

input [3:0] operation;

input clk;

output[15:0] out;

reg [15:0] out;

always@(posedge clk)

begin

case(operation)

4'b0010:

out <= in1+in2;

4'b0011:

out <= in1-in2;

4'b0100:

out <= !in1;

4'b0101:

out <= in1<<in2;

4'b0110:

out <= in1>>in2;

4'b0111:

out <= in1&in2;

4'b1000:

out <= in1|in2;

//4'b1001:

// out = in1>=in2?16'd0:16'd1;

default: out <= 16'hFFFF;

endcase

end

endmodule

My testbench is as follows

module test_projectALU;

reg [15:0] in1;

reg [15:0] in2;

reg [3:0] operation;

reg [15:0] out;

reg clk;

ALU PA(in1,in2,operation,out);

initial

begin

operation=4'b0000;

in1=4'b0000;

in2=4'b0000;

clk = 0;

end

always

begin

#2 operation=4'b0010; in1=4'b0011; in2=4'b0000;

#2 operation=4'b0011; in1=4'b0001; in2=4'b0011;

#2 operation=4'b0000; in1=4'b1100; in2=4'b1101;

#2 operation=4'b0011; in1=4'b1100; in2=4'b1101;

end

always

begin

#5 clk=~clk;

end

initial $monitor($time,"f=%b, a=%b, b=%b,c=%b",operation,in1,in2,out);

//initial #10 $stop;

endmodule

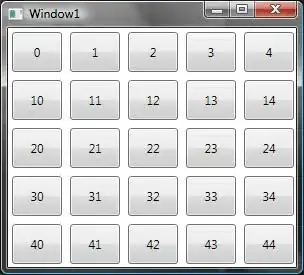

My output for simulation is attached as image.

Why is that the output is not defined (X state) ? What am I doing wrong?