As you can imagine by seeing my code right there, I'm a beginner at VHDL so I'm really wondering why this isn't working as it seems it logically should work.

In fact the part that isn't behaving the way that I'd like it to isn't doing anything at all.

To make this a bit more simple to understand, I'll explain at least a bit what this is supposed to do. First, the IN port New_Data indicates on 1 that a new data is available and should be evaluated. The input Code is the value to evaluate/interpret. The output is the new speed value and current is the current/previous one. Direction is inverted by input code 10.

The part that doesn't work or actually do anything: If the code is + (val 43) you increase it by 1, if the code is - (val 45) you reduce it by 1 then the result it sent to the speed output.

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.NUMERIC_STD.ALL;

ENTITY Code_Interpret IS

PORT (

New_Data: IN STD_LOGIC;

Current_Speed: IN UNSIGNED(7 DOWNTO 0);

Code: IN UNSIGNED(7 DOWNTO 0);

Speed: OUT UNSIGNED(7 DOWNTO 0);

Direction: OUT STD_LOGIC

);

END Code_Interpret;

ARCHITECTURE rtl OF Code_Interpret IS

SIGNAL s_speed: UNSIGNED(7 DOWNTO 0):= "00110000";

SIGNAL s_case: INTEGER RANGE 0 TO 64 := 48;

SIGNAL s_direction: STD_LOGIC := '1';

BEGIN

PROCESS (New_Data, Code)

BEGIN

s_case <= TO_INTEGER(Code);

IF RISING_EDGE(New_Data) THEN

CASE s_case IS

WHEN 48 TO 55 =>

--s_speed <= Code;

s_speed <= Code;

WHEN 43 =>

IF Current_Speed < 55 THEN

s_speed <= Current_Speed + 1;

ELSE

s_speed <= Current_Speed;

END IF;

WHEN 45 =>

IF Current_Speed > 48 THEN

s_speed <= Current_Speed - 1;

ELSE

s_speed <= Current_Speed;

END IF;

WHEN 10 =>

s_direction <= NOT s_direction;

WHEN OTHERS =>

NULL;

END CASE;

END IF;

Speed <= s_speed;

Direction <= s_direction;

END PROCESS;

END;

The part that isn't doing what I want:

WHEN 43 =>

IF Current_Speed < 55 THEN

s_speed <= Current_Speed + 1;

ELSE

s_speed <= Current_Speed;

END IF;

WHEN 45 =>

IF Current_Speed > 48 THEN

s_speed <= Current_Speed - 1;

ELSE

s_speed <= Current_Speed;

END IF;

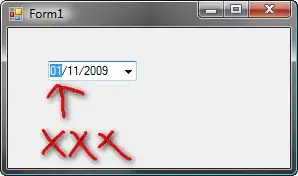

Here is what my simulation looks like. There are 6 markers on the timeline , the first is + then - then a Direction switch and the same codes repeated in the same order.

I've tried a lot of different things but I haven't managed to grasp what the problem is and I'd love to know why this isn't working.

Ok so now I'm simulating only the VHDL code and working straight with the inputs and outputs instead of using useless pins and in a schematic I didn't need. Also I read the Quartus II simulation manual so that helped me fix the radixes. (Like I said, I'm fairly new to this..)

Change in the code to attempt using a VAR:

--....

--SIGNAL s_case: INTEGER RANGE 0 TO 64 := 48;

SIGNAL s_direction: STD_LOGIC := '1';

BEGIN

PROCESS (New_Data, Code)

VARIABLE s_case: INTEGER RANGE 0 TO 64 := 48;

BEGIN

s_case := TO_INTEGER(Code);

IF RISING_EDGE(New_Data) THEN

CASE s_case IS

--....