For the past few days I have been searching for a method of writing a bit of VHDL for a project that will allow me to trigger the processing of a set of data and transmit the results. The device I am using can begin to collect a second set of data while simultaneously serving up the complete first set for my FPGA to transmit, and I want to take advantage of this via pipelining but I haven't been successful.

To trigger the collection I need to send a specific set of signals in a specific order. After a few clock cycles and a signal from the FPGA, the complete set is then output on several ports from the device. My goal is for the whole process to be started by a simple input pulse, and for it to be possible for a second pulse to occur while the assignments from the first pulse are still occuring. Is there a way for me to send the first set of signals, and then later the signal to output the data while simultaneously sending the first set of signals for the second collection, if that makes sense?

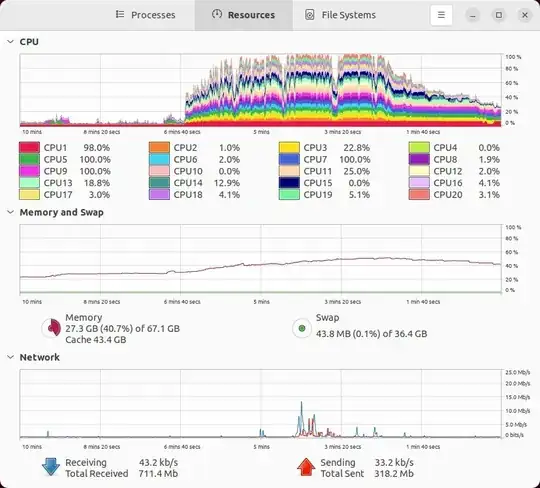

Here's a picture of what I mean.

As you can see, the data from integration 1 is sent during the second and even third integration stage. load_pulse is the signal that requests the data to be output on DATA, and it can occur much later while the second set of signals for integration 2 are sent.

Here's a bit of test VHDL that I wrote to see if it was possible with a simple process:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity test is

port(

x : in STD_LOGIC;

y : out STD_LOGIC := '0';

z : out STD_LOGIC := '0'

);

end test;

architecture test_behav of test is

begin

process(x) is

begin

y <= '0', '1' after 10 NS, '0' after 20 ns;

z <= '0', '1' after 30 NS, '0' after 40 ns;

end process;

end test_behav;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity testbench is

end testbench;

architecture testbench_behav of testbench is

component test is

port(

x : in STD_LOGIC;

y : out STD_LOGIC;

z : out STD_LOGIC

);

end component test;

signal x : STD_LOGIC := '0';

signal y : STD_LOGIC := '0';

signal z : STD_LOGIC := '0';

begin

testo: component test

port map(

x => x,

y => y,

z => z

);

x <= '1' after 25 ns;

end testbench_behav;

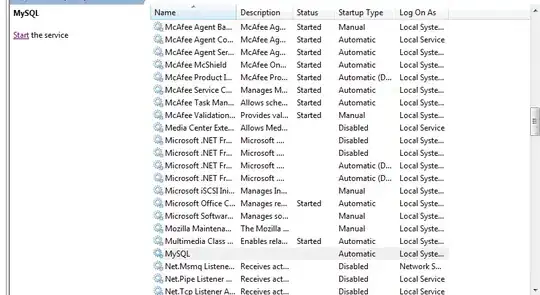

In this example, I trigger the process while its signal assignments are still executing. The result here was that the original signal assignments were interrupted and the new signal assignments completed after x <= '1' after 25 ns, as you can see here:

Is there a way to accomplish this that you can explain to me or point me to an explanation of, or will I need to take another approach?

Thanks