I'm a newbie in VHDL and hardware world. I'm trying to make a Count&Compare example using Top Level Hierarchy and test it with testbench and see the results on ISIM.

Here is my block diagram sketch:

So I end up these 3 vhd source files:

Counter.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Count_src is

Port ( CLK : in STD_LOGIC;

Reset : in STD_LOGIC;

S : out STD_LOGIC_VECTOR (3 downto 0));

end Count_src;

architecture Behavioral of Count_src is

signal count : STD_LOGIC_VECTOR (3 downto 0);

begin

process (Reset, CLK)

begin

if Reset = '1' then -- Active high reset

count <= "0000"; -- Clear count to 0

elsif (rising_edge(CLK)) then -- Positive edge

count <= count + "0001"; -- increment count

end if;

end process;

S <= count; -- Export count

end Behavioral;

Compare

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity Compare_src is

Port ( A : in STD_LOGIC_VECTOR (3 downto 0);

B : in STD_LOGIC_VECTOR (3 downto 0);

S : out STD_LOGIC);

end Compare_src;

architecture Behavioral of Compare_src is

begin

S <= '1' when (A = B) else -- Test if A and B are same

'0'; -- Set when S is different

end Behavioral;

CountCompare (Top Level)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity CountCompare_src is

Port ( Clock : in STD_LOGIC;

Reset : in STD_LOGIC;

Value : in STD_LOGIC_VECTOR (3 downto 0);

Flag : out STD_LOGIC);

end CountCompare_src;

architecture Behavioral of CountCompare_src is

-- COMPONENT DECLERATIONS

component counter is

port ( CLK : in std_logic;

Reset : in std_logic;

S : out std_logic_vector(3 downto 0)

);

end component;

component compare is

port (A : in std_logic_vector(3 downto 0);

B : in std_logic_vector(3 downto 0);

S : out std_logic

);

end component;

-- Component Spesification and Binding

for all : counter use entity work.Count_src(behavioral);

for all : compare use entity work.Compare_src(behavioral);

-- Internal Wires

signal count_out : std_logic_vector(3 downto 0);

begin

-- Component instantiation

C1: counter PORT MAP ( Reset => Reset,

CLK => Clock,

S => count_out

);

C2: compare PORT MAP ( A => count_out,

B => Value,

S => Flag

);

end Behavioral;

To test the design I wrote a testbench as follows:

TestBench

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY TopLevelTester_tb IS

END TopLevelTester_tb;

ARCHITECTURE behavior OF TopLevelTester_tb IS

--Input and Output definitions.

signal Clock : std_logic := '0';

signal Reset : std_logic := '0';

signal Value : std_logic_vector(3 downto 0) := "1000";

signal Flag : std_logic;

-- Clock period definitions

constant clk_period : time := 1 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: entity work.CountCompare_src PORT MAP

(

Clock => Clock,

Reset => Reset,

Value => Value

);

proc: process

begin

Clock <= '0';

wait for clk_period/2;

Clock <= '1';

wait for clk_period/2;

end process;

END;

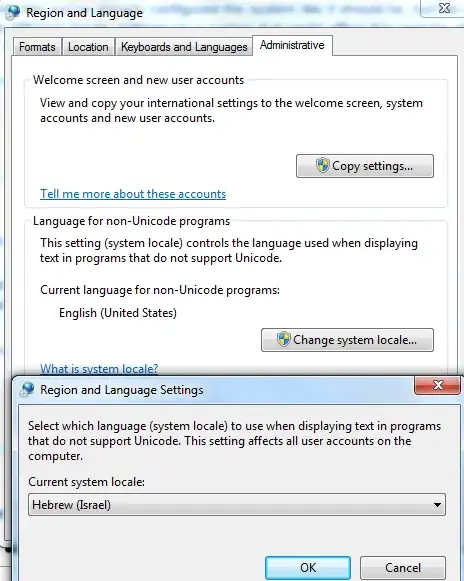

When I simulate behavioral model, the ISIM pops up, but I see no changes on the Compare Flag. Here is the ss of the ISIM:

What am I missing here? Why does'nt the Flag change?

My best regards.