Everywhere it is mentioned this as a guideline, but after lot of thought i want to know what harm will it cause if we use Nonblocking statement inside Always Block for Combinatorial also. I won't be mixing the two together. But what i feel is when we use Nonblocking for Combinatorial statements in Always Block it represents the hardware more accurately. Does it not...?

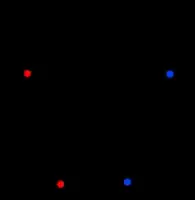

For Example, if we take the following circuit:

In this diagram when the inputs a,b,c are supplied the outputs x1 and x will not be available instantly. There will be gate delays. first x1 will be available and then x will be available. If we use blocking statements both are available instantly. If we use nonblocking, it resembles the hardware more accurately.

For Example, if we take the following code based on the above diagram

module block_nonblock(output logic x,x1,y,y1,input logic a,b,c);

always@* begin : BLOCKING

x1 = a & b;

x = x1 & c;

end

always@* begin : NONBLOCKING

y1 <= a & b;

y <= y1 & c;

end

endmodule

This synthesizes as:

Both are synthesized as And gates, and give same simulation results but when we check for the changes in output in delta time, i feel the Non blocking matches the hardware more accurately as compared to the Blocking.

Also i went through : IEEE P1364.1 / D1.6 Draft Standard for Verilog® Register Transfer Level Synthesis, which specifies the use of non blocking for Sequential modeling but doesn't specify specifically using blocking for Combinational modeling using Always Block. It says don't mix the two(Blocking and Nonblocking) in Combinational statements.

So, shouldn't we use nonblocking for combinational statements in always blocks which are dealing with pure combi logic (non sequential/ no clocks involved)