I am trying to create an ALU using structural code in VHDL. The code was originally in Verilog and then I manually changed it all over to VHDL, so that's why I have many separate files...but in theory these should work. The following are the associated codes and files:

--dwl_fulladd code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_fulladd IS

PORT (

x, y, Cin: IN STD_LOGIC;

s, Cout: OUT STD_LOGIC);

END dwl_fulladd;

ARCHITECTURE Structural OF dwl_fulladd IS

BEGIN

s <= x XNOR y XNOR Cin;

Cout <= ((x AND y) OR (x AND Cin) OR (y AND Cin));

END Structural;

--dwl_4bitadder code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_4bitadder IS

PORT (

x, y : IN STD_LOGIC_VECTOR (3 DOWNTO 0);

carryin: IN STD_LOGIC;

s: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END dwl_4bitadder;

ARCHITECTURE Structural OF dwl_4bitadder IS

SIGNAL c : STD_LOGIC_VECTOR (3 DOWNTO 1);

COMPONENT dwl_fulladd

PORT (

x, y, Cin: IN STD_LOGIC;

s, Cout: OUT STD_LOGIC);

END COMPONENT dwl_fulladd;

BEGIN

stage0: dwl_fulladd PORT MAP (carryin, x(0), y(0), s(0), c(1));

stage1: dwl_fulladd PORT MAP (c(1), x(1), y(1), s(1), c(2));

stage2: dwl_fulladd PORT MAP (c(2), x(2), y(2), s(2), c(3));

stage3: dwl_fulladd PORT MAP (c(3), x(3), y(3), s(3), carryout);

END Structural;

--dwl_mux2to1 code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_mux2to1 IS

PORT (

x1, x2, s: IN STD_LOGIC;

f: OUT STD_LOGIC);

END dwl_mux2to1;

ARCHITECTURE Structural OF dwl_mux2to1 IS

BEGIN

f <= (((NOT s)AND x1)OR(s AND x2));

END Structural;

--dwl_4mux2to1 code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_4mux2to1 IS

PORT (

x0, x1: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sel: IN STD_LOGIC;

f: OUT STD_LOGIC_VECTOR (3 DOWNTO 0));

END dwl_4mux2to1;

ARCHITECTURE Structural OF dwl_4mux2to1 IS

COMPONENT dwl_mux2to1 IS

PORT (

x1, x2, s: IN STD_LOGIC;

f: OUT STD_LOGIC);

END COMPONENT dwl_mux2to1;

BEGIN

stage0: dwl_mux2to1 PORT MAP (sel, x0(0), x1(0), f(0));

stage1: dwl_mux2to1 PORT MAP (sel, x0(1), x1(1), f(1));

stage2: dwl_mux2to1 PORT MAP (sel, x0(2), x1(2), f(2));

stage3: dwl_mux2to1 PORT MAP (sel, x0(3), x1(3), f(3));

END Structural;

--dwl_Blogic code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_Blogic IS

PORT (

FS2_in, FS1_in: IN STD_LOGIC;

B_in: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

Y_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0));

END dwl_Blogic;

ARCHITECTURE Behavioral OF dwl_Blogic IS

BEGIN

PROCESS (FS2_in, FS1_in, B_in)

BEGIN

if FS2_in = '0' AND FS1_in = '0' then

Y_out <= "0000";

elsif FS2_in = '0' AND FS1_in = '1' then

Y_out <= B_in;

elsif FS2_in = '1' AND FS1_in = '0' then

Y_out <= (NOT B_in);

elsif FS2_in = '1' AND FS1_in = '1' then

Y_out <= "1111";

end if;

END PROCESS;

END Behavioral;

-dwl_lu code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_lu IS

PORT (

FS: IN STD_LOGIC_VECTOR (2 DOWNTO 1);

A, B: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

lu_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END dwl_lu;

ARCHITECTURE Behavioral OF dwl_lu IS

BEGIN

PROCESS (FS, A, B)

BEGIN

if FS = "00" then

lu_out <= (Not A);

carryout <= '0';

elsif FS = "01" then

lu_out <= (A AND B);

carryout <= '0';

elsif FS = "10" then

lu_out <= (A OR B);

carryout <= '0';

elsif FS = "11" then

lu_out <= (A(3) & A(3) & A(2) & A(1));

carryout <= A(0);

END if;

END PROCESS;

END Behavioral;

--dwl_au code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_au IS

PORT (

FS: IN STD_LOGIC_VECTOR (2 DOWNTO 0);

A, B: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

au_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END dwl_au;

ARCHITECTURE Structural OF dwl_au IS

SIGNAL Y: STD_LOGIC_VECTOR (3 DOWNTO 0);

COMPONENT dwl_Blogic IS

PORT (

FS2_in, FS1_in: IN STD_LOGIC;

B_in: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

Y_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0));

END COMPONENT dwl_Blogic;

COMPONENT dwl_4bitadder IS

PORT (

x, y : IN STD_LOGIC_VECTOR (3 DOWNTO 0);

carryin: IN STD_LOGIC;

s: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END COMPONENT dwl_4bitadder;

BEGIN

stage0: dwl_Blogic (FS(2), FS(1), B, Y);

stage1: dwl_4bitadder (FS(0), A, Y, au_out, carryout);

END Structural;

--dwl_alu code--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_signed.all;

ENTITY dwl_alu_vhdl IS

PORT (

FS, A, B: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

F: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

Cout: OUT STD_LOGIC);

END dwl_alu_vhdl;

ARCHITECTURE Structural OF dwl_alu_vhdl IS

SIGNAL AU, LU: STD_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL AU_C, LU_C: STD_LOGIC;

COMPONENT dwl_au IS

PORT (

FS: IN STD_LOGIC_VECTOR (2 DOWNTO 0);

A, B: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

au_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END COMPONENT dwl_au;

COMPONENT dwl_lu IS

PORT (

FS: IN STD_LOGIC_VECTOR (2 DOWNTO 1);

A, B: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

lu_out: OUT STD_LOGIC_VECTOR (3 DOWNTO 0);

carryout: OUT STD_LOGIC);

END COMPONENT dwl_lu;

COMPONENT dwl_4mux2to1 IS

PORT (

x0, x1: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

sel: IN STD_LOGIC;

f: OUT STD_LOGIC_VECTOR (3 DOWNTO 0));

END COMPONENT dwl_4mux2to1;

COMPONENT dwl_mux2to1 IS

PORT (

x1, x2, s: IN STD_LOGIC;

f: OUT STD_LOGIC);

END COMPONENT dwl_mux2to1;

BEGIN

stage0: dwl_au (FS(2 DOWNTO 0), A, B, AU, AU_C);

stage1: dwl_lu (FS(2 DOWNTO 1), A, B, LU, LU_C);

stage2: dwl_4mux2to1 (FS(3), AU, LU, F);

stage3: dwl_mux2to1 (FS(3), AU_C, LU_C, Cout);

END Structural;

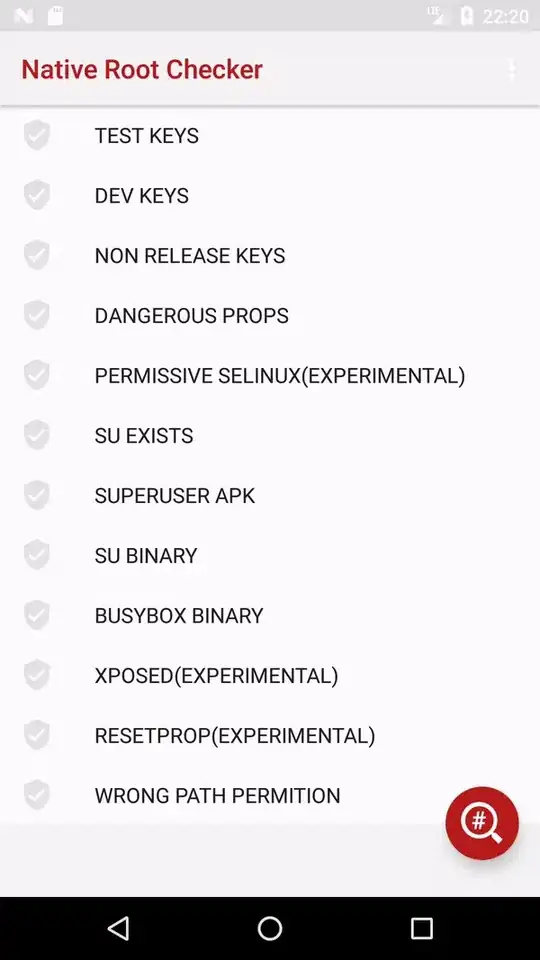

This is the truth table for the Logic unit:

This is the truth table for the BLogic Unit:

I keep on getting the following errors:

Error (10777): VHDL error at nwl_au.vhd(34): expected an architecture identifier in index.

Error (10346): VHDL error at nwl_au.vhd(34): formal port or parameter "FS2_in" must have actual or default value.

Error (10784): HDL error at nwl_au.vhd(19): see declaration for object "FS2_in".

Error (10346): VHDL error at nwl_au.vhd(34): formal port or parameter "FS1_in" must have actual or default value.

Error (10784): HDL error at nwl_au.vhd(19): see declaration for object "FS1_in".

Error (10346): VHDL error at nwl_au.vhd(34): formal port or parameter "B_in" must have actual or default value.

Error (10784): HDL error at nwl_au.vhd(20): see declaration for object "B_in".

These errors are pertaining to the dwl_au poetion of the code.

Could someone help out with this? I don't know how to fix it.