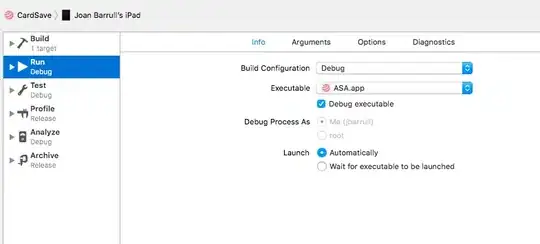

I have a 8192 row (13 bit address) and 12 bit width block ram.

In Virtex-6, we have 36kb Block Rams. So ISE Design Suite implements my ram as three 36kb BRAM with 4 bit width.

For timing issues, I want ISE to use individual flip-flops for each BRAM read/write address. So for read/write address reg I set properties but they are not applied.