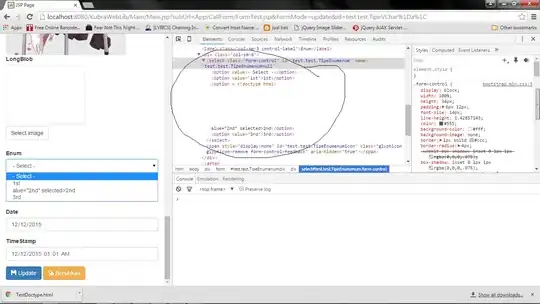

I'm starting to write a VGA controller for a DE0 board. I have a model which compiles and loads onto the DE0 board. Also it displays the test message. The problem I am having is I cannot simulate my controller using Quartus II modsim. When I run the simulation I cannot start the VGA file. The little plus icon is missing from the file. A picture and the models file I am using are below:

vga model

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY VGA is

PORT (clk : IN std_logic; -- demo had 2 bit vector

rst : IN std_logic:='1';

vga_hs, vga_vs : OUT std_logic;

vga_r, vga_g, vga_b : OUT std_logic_vector(3 DOWNTO 0));

END ENTITY VGA;

ARCHITECTURE A1 OF VGA IS

SIGNAL clk25 : std_logic; -- clk25 signal

BEGIN

SYNC1 : ENTITY work.sync(A1)

PORT MAP (clk25, vga_hs, vga_vs, vga_r, vga_g, vga_b);

CLK_25 : ENTITY work.CLK25(behav)

PORT MAP (clk, rst, clk25);

END ARCHITECTURE A1;

Sync model

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.numeric_std.ALL;

ENTITY SYNC IS

GENERIC (

h_res : integer:= 640 ; -- horizontal screen resolution

h_fp : integer:= 16 ; -- horizontal front porch

h_bp : integer:= 48 ; -- horizontal back porch

h_sync : integer:= 96 ; -- horizontal sync pulse duration

h_sync_pol : std_logic:='0'; -- horizontal sync pulse state

v_res : integer:= 480 ; -- vertical screen resolution

v_fp : integer:= 10 ; -- vertical front porch

v_bp : integer:= 33 ; -- vertical back porch

v_sync : integer:= 2; -- vertical sync pulse duration

v_sync_pol : std_logic:='0' -- vertical sync pulse state

);

PORT(

clk : IN std_logic;

h_sync_pulse, v_sync_pulse : OUT std_logic;

r, g, b : OUT std_logic_vector(3 DOWNTO 0)

);

END ENTITY SYNC;

ARCHITECTURE A1 OF SYNC IS

CONSTANT h_size : integer := (h_res + h_fp + h_bp + h_sync); -- total horizontal vector

CONSTANT v_size : integer := (v_res + v_fp + v_bp + v_sync); -- total vertical vector

SIGNAL h_pos : integer RANGE 0 TO h_size := 0; -- total horizontal vector

SIGNAL v_pos : integer RANGE 0 TO h_size := 0; -- total vertical vector

BEGIN

TIMING :PROCESS(clk, h_pos, v_pos) IS

BEGIN

IF rising_edge(clk) THEN

IF (h_pos <= 480 or v_pos <= 285) THEN -- middle of the screen is pic res/2 + (FP + sync + BP)

r <= (OTHERS => '1');

g <= (OTHERS => '1');

b <= (OTHERS => '1');

ELSE

r <= (OTHERS => '0');

g <= (OTHERS => '0');

b <= (OTHERS => '0');

END IF;

IF (h_pos <= 480 or v_pos <= 285) THEN -- middle of the screen is pic res/2 + (FP + sync + BP)

r <= (OTHERS => '1');

g <= (OTHERS => '1');

b <= (OTHERS => '1');

ELSE

r <= (OTHERS => '0');

g <= (OTHERS => '0');

b <= (OTHERS => '0');

END IF;

IF (h_pos < h_size) THEN

h_pos <= h_pos + 1;

ELSE

h_pos <= 0;

IF (v_pos < v_size) THEN

v_pos <= v_pos + 1;

ELSE

v_pos <= 0; --< edit was v_pos <= v_pos

END IF;

END IF;

IF (h_pos > h_fp and h_pos < h_fp + h_sync ) THEN -- H_POS between end of FP and the end of H_SYNC

h_sync_pulse <= h_sync_pol; -- H_SYNC needs to stay high during display

ELSE

h_sync_pulse <= '1';

END IF;

IF (v_pos > v_fp and v_pos < v_fp + v_sync ) THEN --V_POS between end of FP and the end of V_SYNC

v_sync_pulse <= v_sync_pol; -- V_SYNC needs to stay high during display

ELSE

v_sync_pulse <= '1';

END IF;

IF ((h_pos > 0 and h_pos < h_fp + h_bp + h_sync) or (v_pos > 0 and v_pos < v_fp + v_bp + v_sync )) THEN --During all of SYNC i.e FP + SYNC + BP colour signals stay low

r <= (OTHERS => '0');

g <= (OTHERS => '0');

b <= (OTHERS => '0');

END IF;

END IF;

END PROCESS TIMING;

END ARCHITECTURE A1;

The design units after compilation do not show the architectures for either the vga.vhd or the sync.vhd files