After discussion with Russel in the comments, I found out, that some points in my original and accepted answer were wrong. Of course, Quartus-II supports an initial high value for flip-flops after power-up, but, the actual mapping on Altera FPGAs causes a difference between ModelSim and SignalTap.

The programmable flip-flops on all Altera FPGAs (as of 2016) can only by initialized to zero as stated in the Quartus Prime Pro Edition Handbook Volume 1: Design and Synthesis in Section 11 "Recommended HDL Coding Styles":

Registers in the device core always power up to a low (0) logic level on all Altera devices.

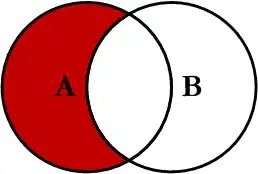

An initial value of high (1) logic level is emulated on Altera FPGAs by inverting the flip-flop (FF) data input and output and then initializing the FF to low instead of high as also described in the Section 11. Thus, the description of this FF:

library ieee;

use ieee.std_logic_1164.all;

entity FF_init1 is

port (D, CLK : in std_logic;

Q : out std_logic);

end FF_init1;

architecture rtl of FF_init1 is

signal FF : std_logic := '1';

begin

FF <= D when rising_edge(CLK);

Q <= FF;

end rtl;

will be mapped like this:

Don't overlook the inverter on the D input of the FF. After power-up the FF itself is initialized to low, but due the negation of the Q output afterwars, it behaves as an initialization to high of the output Q of the entity FF_init1. During run-time, the FF stores the negated input at the rising clock-edge, which is again negated at the output.

The inverter at the output might be merged into the subsequent logic, so that, you cannot always connect SignalTap after the output inverter. Often, you can only connect SignalTap to the FF output itself, but this wire has an opposite logic level to the signal value of FF within ModelSim.